Fundamentals of Electronic Circuits and Systems II

# Wrap Up

Milin Zhang Dept of EE, Tsinghua University

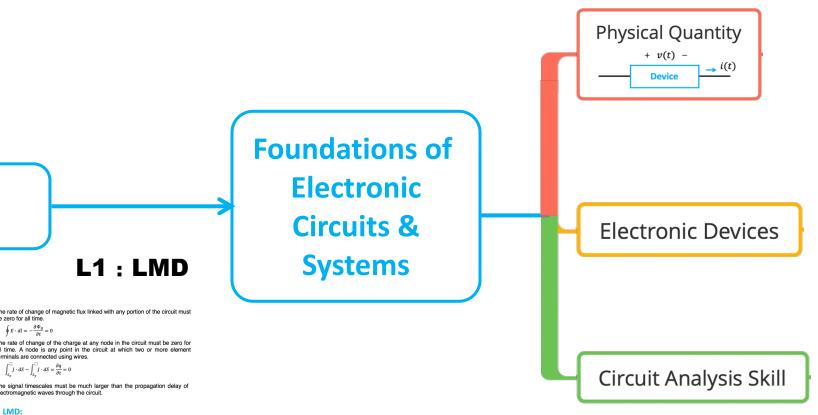

The rate of change of magnetic flux linked with any portion of the circuit must be zero for all time.

$$\oint E \cdot dl = -\frac{\partial \Phi_B}{\partial t} = 0$$

The rate of change of the charge at any node in the circuit must be zero for all time. A node is any point in the circuit at which two or more element terminals are connected using wires.

$$\int_{S_x}^{\Box} J \cdot dS - \int_{S_y}^{\Box} J \cdot dS = \frac{\partial q}{\partial t} = 0$$

• The signal timescales must be much larger than the propagation delay of electromagnetic waves through the circuit.

#### LMD:

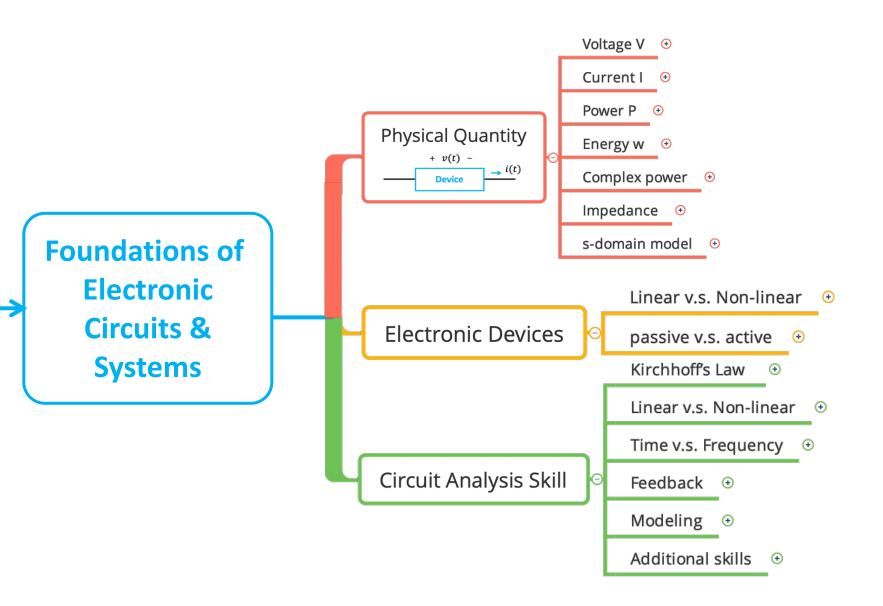

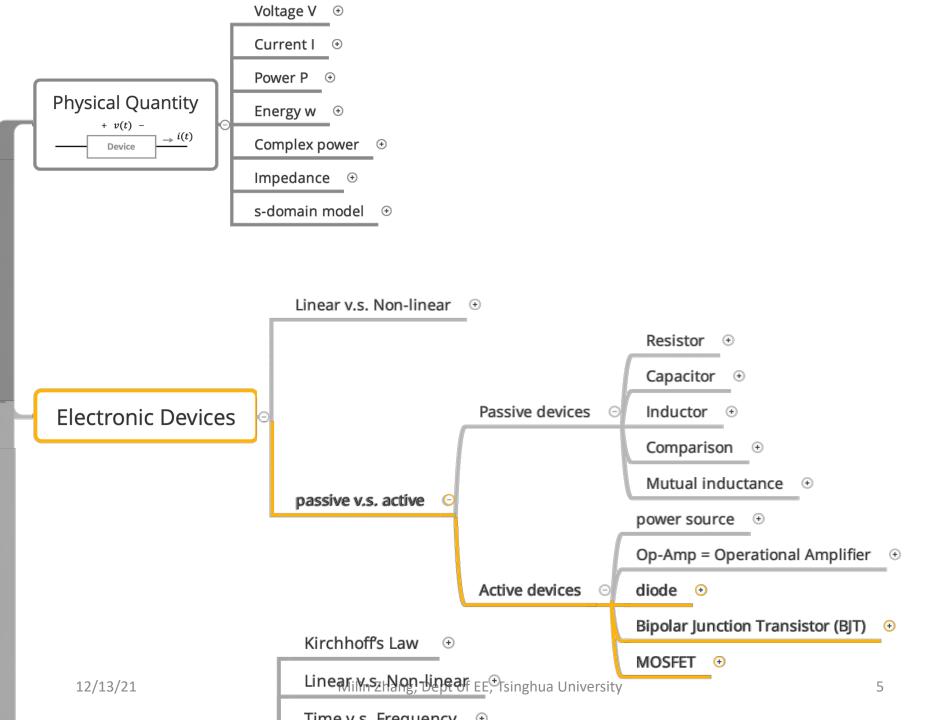

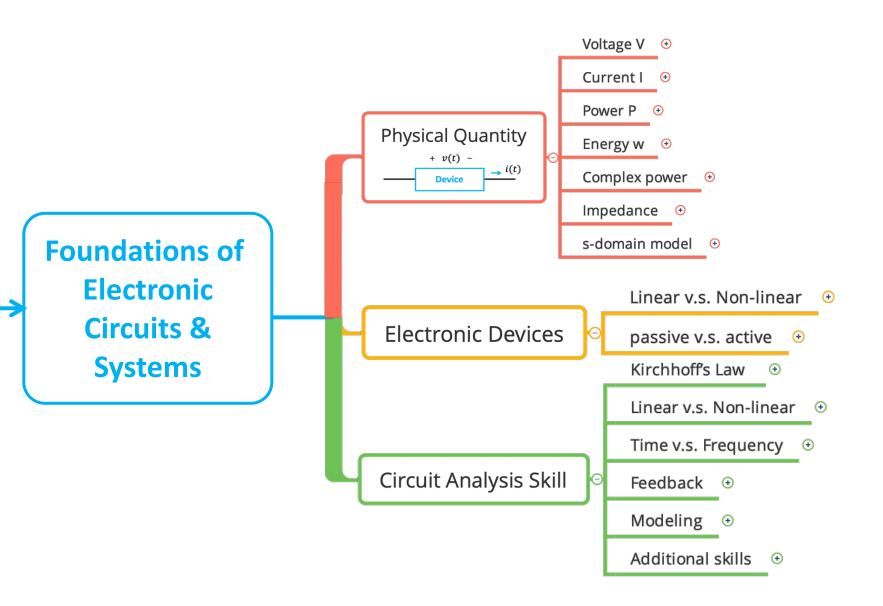

#### The fundamental of circuit and system theory

The fundamental of circuit and system theory

# **High Performance IP & New Devices**

Nan Sun

**Huaqiang Wu**

| System             | Device                  | IP                      | Made in<br>China % |

|--------------------|-------------------------|-------------------------|--------------------|

| Computing          | Server                  | MPU                     | 0%                 |

|                    | РС                      | MPU                     | 0%                 |

|                    | For industry            | MCU                     | 2%                 |

| General<br>Purpose | Programmable            | FPGA/EPLD               | 0%                 |

|                    | DSP                     | DSP                     | 0%                 |

| Communication      | Mobile                  | Application processor   | 18%                |

|                    |                         | Communication Processor | 22%                |

|                    |                         | Embedded MPU            | 0%                 |

|                    |                         | Embedded DSP            | 0%                 |

|                    | Network                 | NPU                     | 15%                |

| Memory             | Semiconductor<br>Memory | DRAM                    | 0%                 |

|                    |                         | NAND Flash              | 0%                 |

|                    |                         | NOR Flash               | 5%                 |

| Display            | TV                      | Image processor         | 5%                 |

|                    |                         | Display driver          | 0%                 |

# **Processing Unit (PU) & AI**

intel)

Yu Wang

Yongpan Liu

Shouyi Yin

Movidius

### **Intelligent Micro-System**

**Huazhong Yang**

Smaller volume size Higher capability Higher performance

NEURALINK

To bridge the brain to man-made devices

Milin Zhang

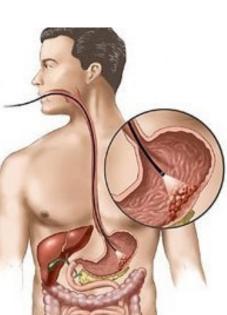

#### **Smart Sensing**

### **Bio-Medical & Healthcare**

Guolin Li

Zhihua Wang

Hong Chen

V.S.

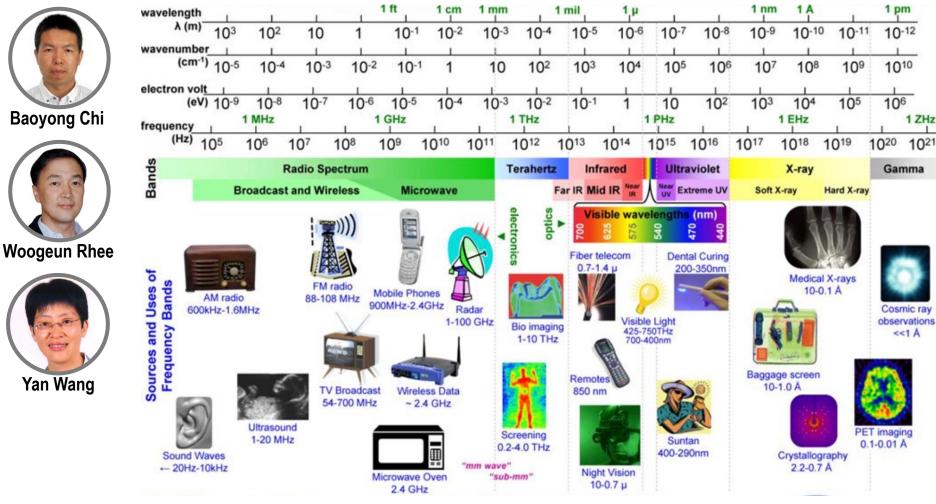

### **Radio Frequency Circuits & Application**

#### © Dong-Yo Jheng

#### **Final Exam**

- Date: Jan 6<sup>th</sup> 2022

- Time: 9:00am 11:00am

- Location: 6A203