# **Bipolar Junction Transistors**

Milin Zhang Dept of EE, Tsinghua University

### BJT – a milestone in IC history

#### **Bipolar Junction Transistor = BJT**

First Transistor @ 1947

William Shockley

John Bardeen

Walter Brattain

## BJT – a milestone in IC history

#### **Bipolar Junction Transistor = BJT**

#### **Outline**

- Introduction to BJT

- WHAT does it look like

- HOW does it work

- The characteristic curves

- Circuit analysis techniques with BJT

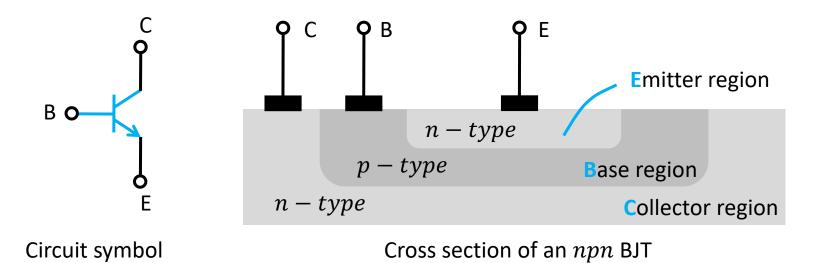

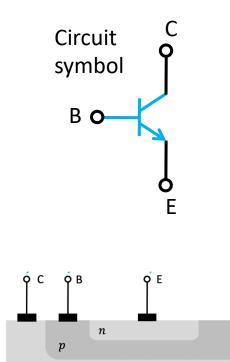

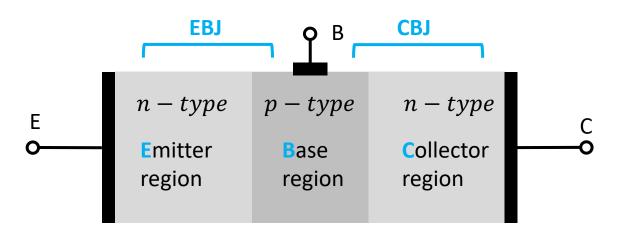

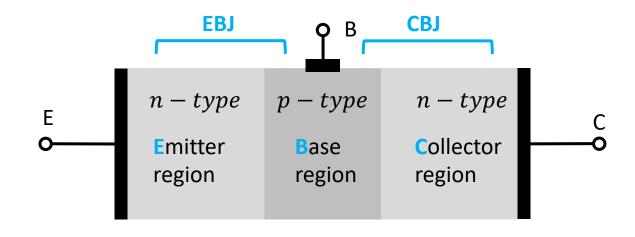

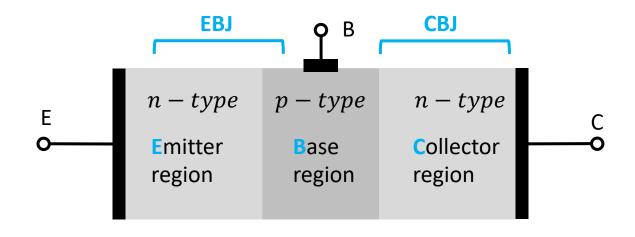

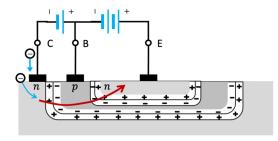

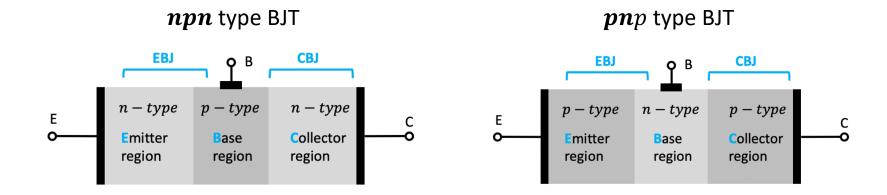

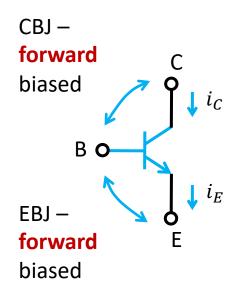

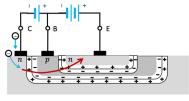

### **Structure of BJT**

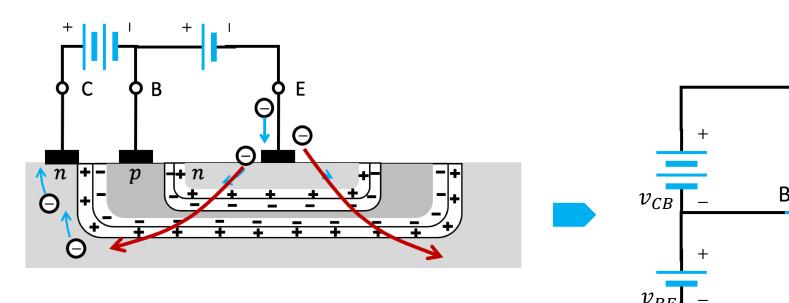

#### **Structure of BJT**

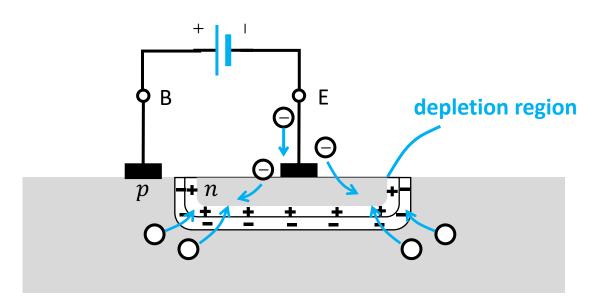

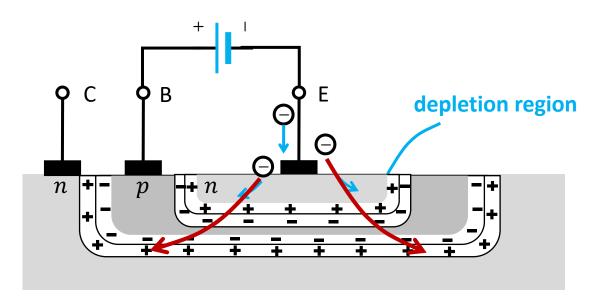

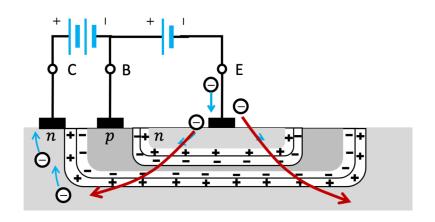

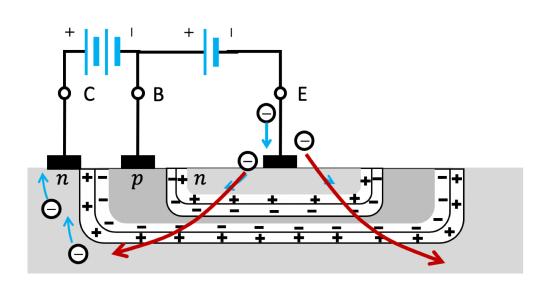

Cross section of an npn BJT

There are 2 pn junctions

- Emitter-base junction (EBJ)

- Collector-base junction (CBJ)

Simplified structure of an npn BJT

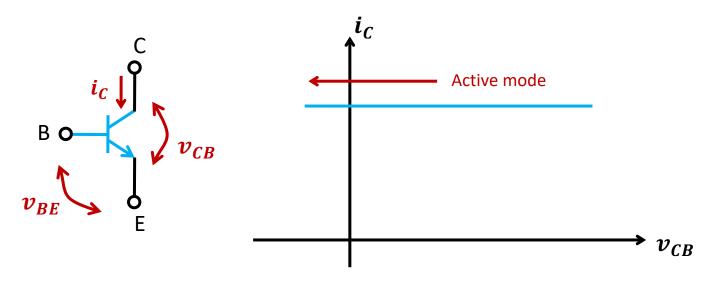

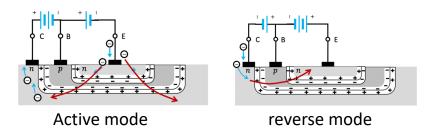

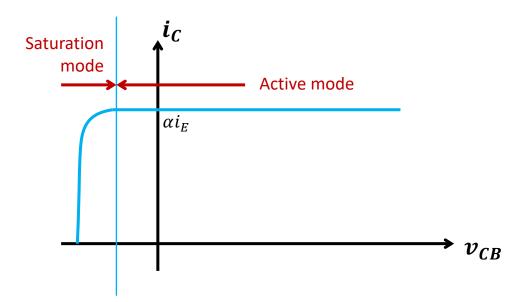

### **BJT** modes of operations

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

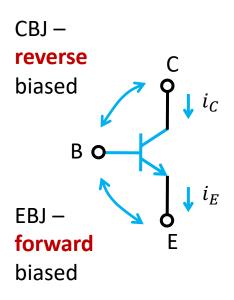

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

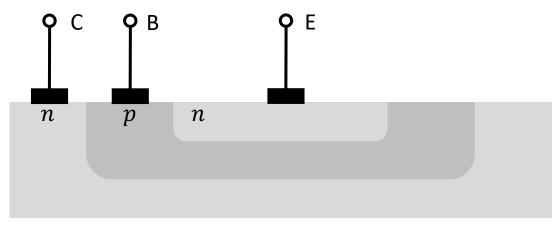

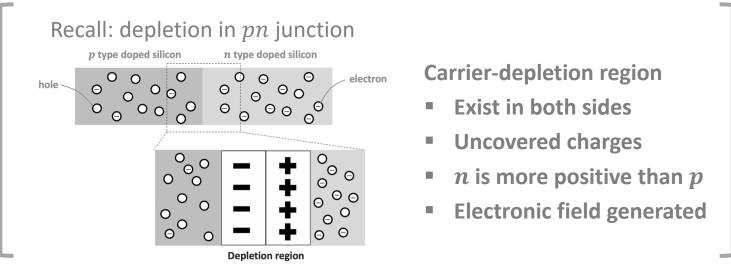

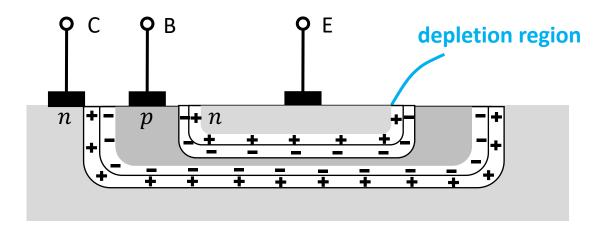

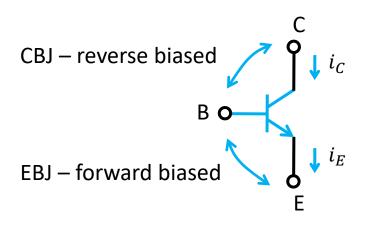

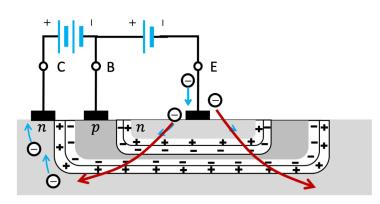

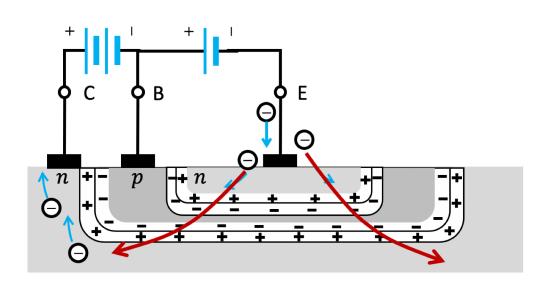

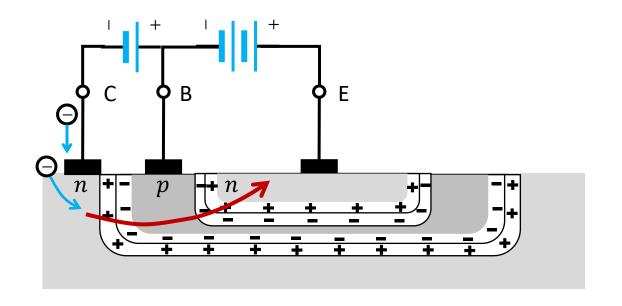

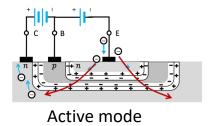

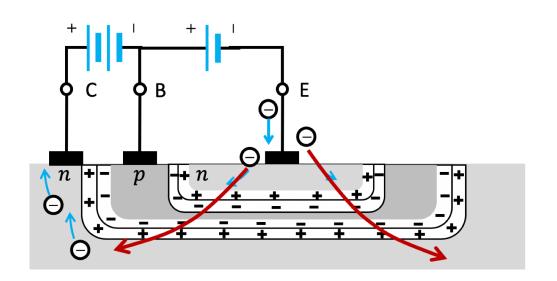

- There are two pn junctions

- Depletion regions are generated in both sides of both EBJ and CBJ

- A forward-bias applied to EBJ

- width of depletion region of EBJ ↓

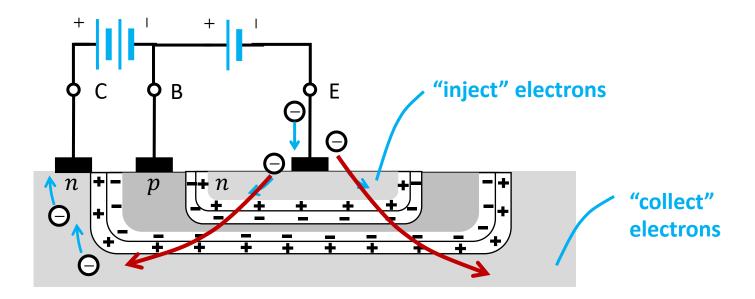

- The base region is very thin. But there are too much electrons ...

- Electrons enter the collector region

- Emitter current is dominated by the electrons

- A reversed-bias applied to CBJ

- Current generated in collector region

- The BJT is biased in **ACTIVE** mode

## **Currents of BJT in active mode**

### **Currents of BJT in active mode**

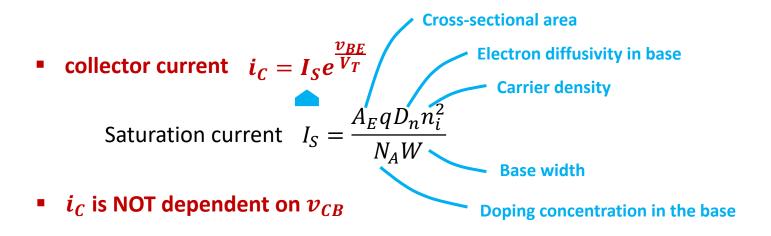

• collector current

$$i_C = I_S e^{\frac{v_{BE}}{V_T}}$$

$\left(I_S = \frac{A_E q D_n n_i^2}{N_A W}\right)$

• base current  $i_B = \frac{i_C}{\beta}$

$$i_B = \frac{A_E q D_p n_i^2}{N_D L_P} e^{\frac{v_{BE}}{V_T}} + \frac{A_E q W n_i^2}{\tau_b N_A} e^{\frac{v_{BE}}{V_T}}$$

Only related to the ~ physical structure of the BJT

$$= \left(\frac{D_p N_A W}{D_n N_D L_P} + \frac{W^2}{2D_n \tau_b}\right) I_S e^{\frac{v_{BE}}{V_T}}$$

$\beta$  – common-emitter current gain typical value of  $\beta$  is 50 – 200

### Summary: BJT in active mode

- collector current  $i_C = I_S e^{\frac{v_{BE}}{V_T}}$

- base current  $i_B = \frac{i_0}{\beta}$

- emitter current  $i_E = i_B + i_C = \frac{\beta + 1}{\beta} i_C = \frac{1}{\alpha} i_C$

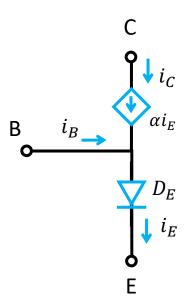

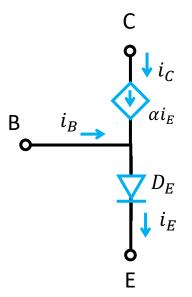

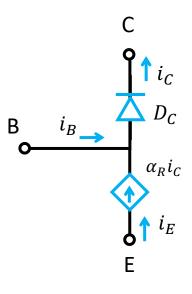

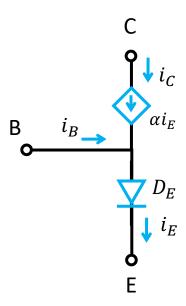

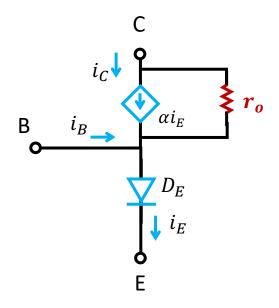

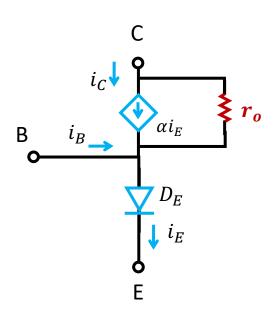

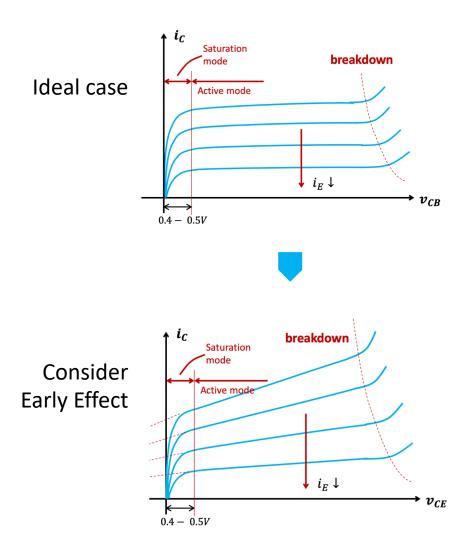

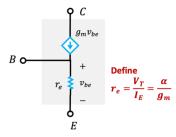

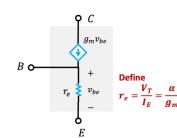

### A model for active mode

### A model for active mode

Since

$$i_C = I_S e^{\frac{v_{BE}}{V_T}}$$

$i_E = I_{SE} e^{\frac{v_{BE}}{V_T}}$   $i_E = \frac{i_C}{\alpha}$

• Thus  $\rightarrow I_{SE} = \frac{I_S}{\alpha}$

## **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Active mode

Active mode

### **Recall: BJT modes of operations**

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

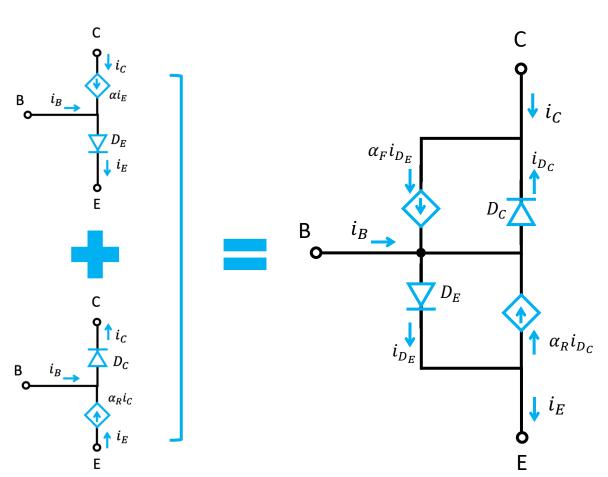

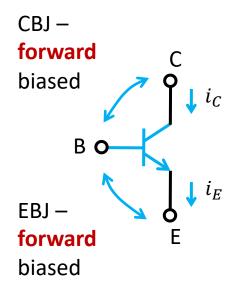

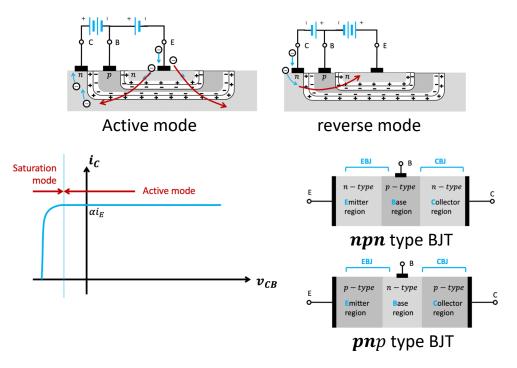

### BJT in reverse mode

- $\alpha_R$  is much lower than  $\alpha$  in active mode

- Typical value of  $\alpha_R$  is 0.01 0.05

$$i_B = \frac{i_E}{\beta_R}$$

$i_E = \alpha_R i_C$

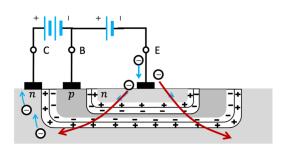

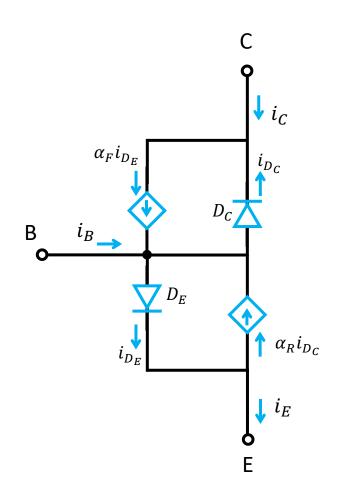

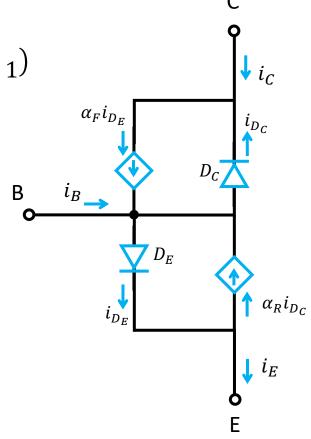

### **EM** model for BJT

Active mode

Reverse mode

### **EM** model for BJT

According to KCL

$$i_C = -i_{D_C} + \alpha_F i_{D_E}$$

• According to i-v characteristics of  $D_E$  and  $D_C$

$$i_{D_C} = I_{SC} \left( e^{\frac{v_{BC}}{V_T}} - 1 \right) = \frac{I_S}{\alpha_R} \left( e^{\frac{v_{BC}}{V_T}} - 1 \right)$$

$$i_{D_E} = I_{SE} \left( e^{\frac{v_{BE}}{V_T}} - 1 \right) = \frac{I_S}{\alpha_F} \left( e^{\frac{v_{BE}}{V_T}} - 1 \right)$$

lacksquare Take  $i_{D_C}$  and  $i_{D_E}$  to  $i_C$

$$i_C = -\frac{I_S}{\alpha_R} \left( e^{\frac{v_{BC}}{V_T}} - 1 \right) + I_S \left( e^{\frac{v_{BE}}{V_T}} - 1 \right)$$

#### **EM** model for BJT

$$\begin{cases} i_{E} = i_{DE} - \alpha_{R} i_{DC} = \frac{I_{S}}{\alpha_{F}} \left( e^{\frac{v_{BE}}{V_{T}}} - 1 \right) - I_{S} \left( e^{\frac{v_{BC}}{V_{T}}} - 1 \right) \\ i_{C} = -i_{DC} + \alpha_{F} i_{DE} = -\frac{I_{S}}{\alpha_{R}} \left( e^{\frac{v_{BC}}{V_{T}}} - 1 \right) + I_{S} \left( e^{\frac{v_{BE}}{V_{T}}} - 1 \right) \end{cases}$$

$$i_C = -\frac{I_S}{\alpha_R} \left( e^{\frac{v_{BC}}{V_T}} - 1 \right) + I_S \left( e^{\frac{v_{BE}}{V_T}} - 1 \right)$$

$$+ \alpha_F I_S \left( e^{\frac{v_{BC}}{V_T}} - 1 \right) - \alpha_F I_S \left( e^{\frac{v_{BC}}{V_T}} - 1 \right)$$

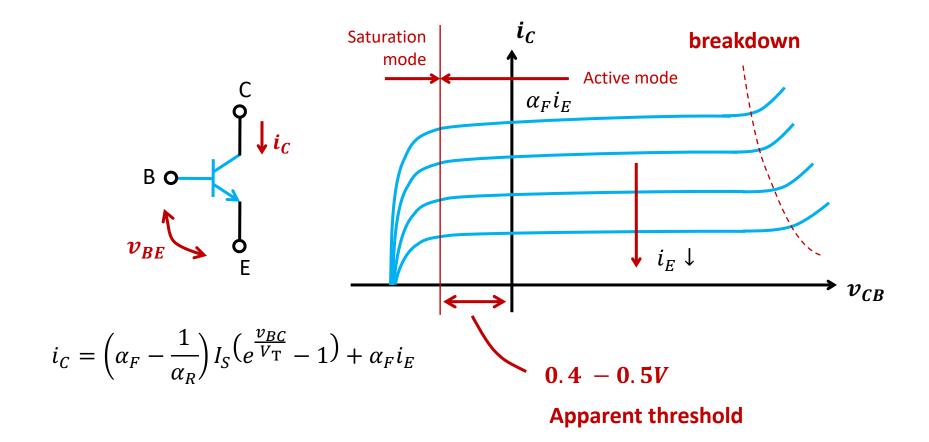

$$= \left(\alpha_F - \frac{1}{\alpha_R}\right) I_S \left(e^{\frac{v_{BC}}{V_T}} - 1\right) + \alpha_F i_E$$

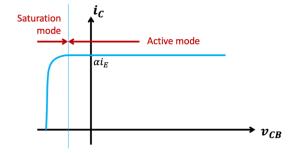

#### **Recall: Currents of BJT in Active Mode**

• collector current

$$i_C = I_S e^{\frac{v_{BE}}{V_T}}$$

Saturation current  $I_S = \frac{A_E q D_n n_i^2}{N_A W}$

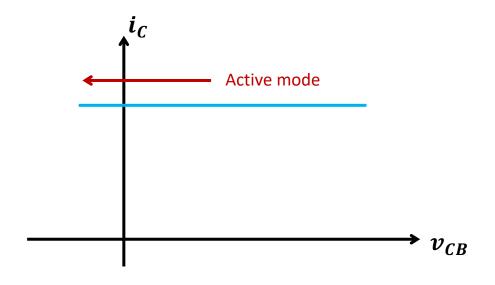

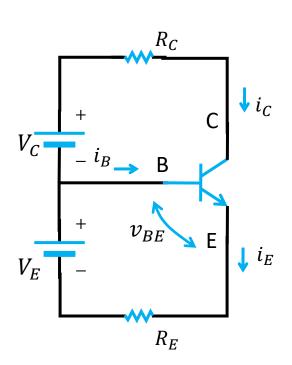

•  $i_C$  is NOT dependent on  $v_{CB}$

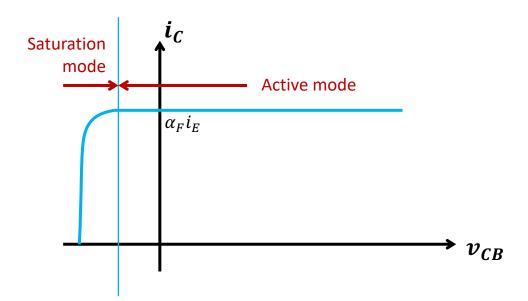

#### **BJT in Saturation Mode**

$$\mathbf{i}_{C} = \left(\alpha_{F} - \frac{1}{\alpha_{R}}\right) I_{S} \left(e^{\frac{\mathbf{v}_{BC}}{V_{T}}} - 1\right) + \alpha_{F} i_{E}$$

When  $v_{BC}$  is increasing  $\rightarrow i_C$  decreases

### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Active mode

- Reverse mode

- Saturation mode

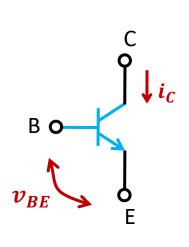

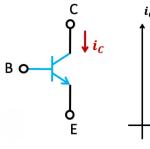

- □ npn v.s. pnp

### npn v.s. pnp

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Active mode

- Reverse mode

- Saturation mode

- □ npn v.s. pnp

Characteristics curves

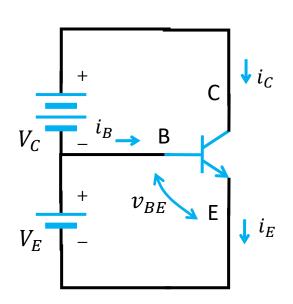

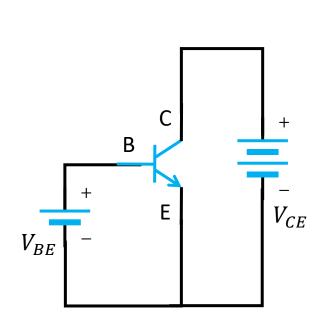

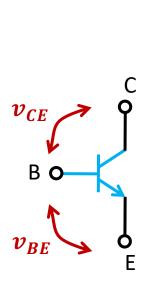

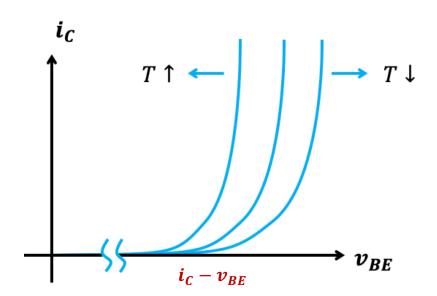

#### From dev. structure to circuit model

$$i_C = I_S e^{rac{v_{BE}}{V_T}}$$

where  $V_T = rac{kT}{q}$

$$i_B = \frac{i_C}{\beta} = \frac{I_S}{\beta} e^{\frac{v_{BE}}{V_T}}$$

$$i_E = rac{i_C}{lpha} = rac{I_S}{lpha} e^{rac{v_{BE}}{V_T}}$$

where  $lpha = rac{eta}{1+eta}$

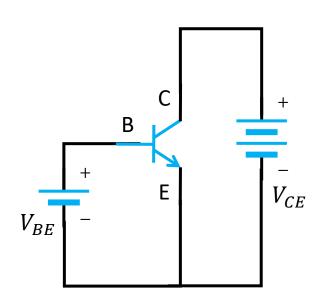

### i - v characteristics

As we already knew, in active mode

$$i_C = \beta i_B$$

$i_E = (1 + \beta) i_B$

- Mathematically  $i_E = i_B + i_C$

- Image the transistor is a super big node

- According to KCL  $i_E = i_B + i_C$

#### KCL/KVL works for transistor circuit anaylsis

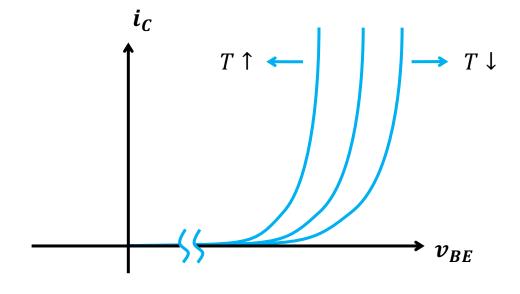

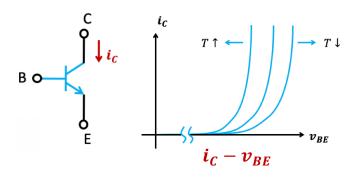

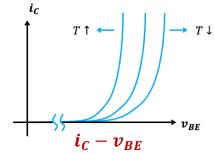

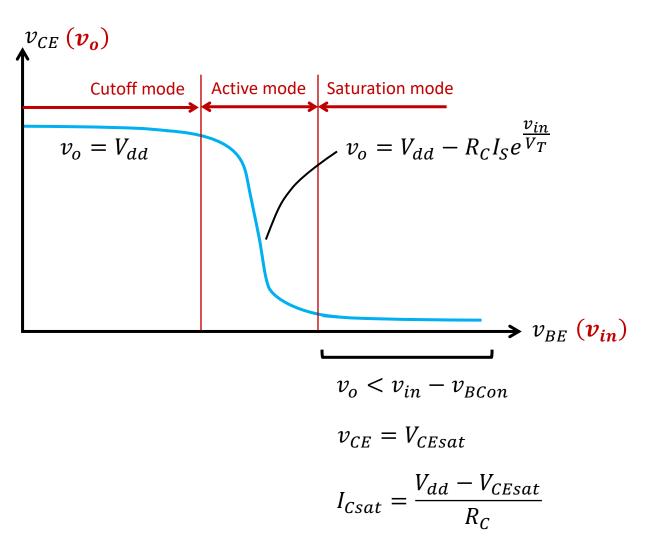

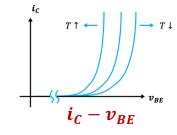

# $i_C - v_{BE}$ characteristics

$$i_C = I_S e^{\frac{v_{BE}}{V_T}}$$

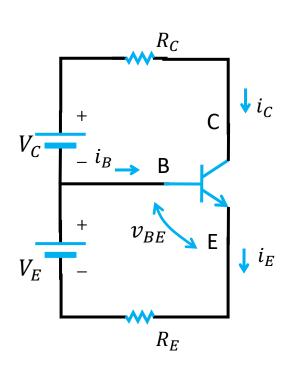

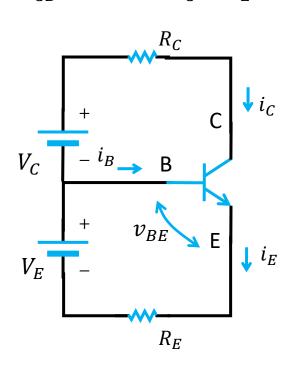

### **Example 1**

**QUESTION:** The transistor has  $\beta=100$  and exhibits a  $v_{BE}$  of 0.7V at  $i_C=1mA$ . Find the resistance of  $R_C$  and  $R_E$  when the transistor is biased in active region at  $i_C=2mA$  and  $v_{CB}=5V$  with  $V_C=V_E=15V$

According to KVL

$$V_C = i_C R_C + v_{CB}$$

$\rightarrow$   $R_C = 5k\Omega$

• According to  $i_C - v_{BE}$  characteristics  $i_C = I_S e^{\frac{v_{BE}}{V_T}}$

Since

$$i_C = 1mA$$

@  $v_{BE} = 0.7V$

$$v_{BE}\Big|_{i_C=2mA} = 0.7 + V_T In\left(\frac{2mA}{1mA}\right) = 0.717V$$

According to KVL

$$V_E = i_E R_E + v_{BE} \qquad \rightarrow \quad i_E R_E = 15.717V$$

### **Example 1**

**QUESTION:** The transistor has  $\beta=100$  and exhibits a  $v_{BE}$  of 0.7V at  $i_C=1mA$ . Find the resistance of  $R_C$  and  $R_E$  when the transistor is biased in active region at  $i_C=2mA$  and  $v_{CB}=5V$  with  $V_C=V_E=15V$

• Since  $\beta = 100$

$$\alpha = \frac{\beta}{\beta + 1} = 0.99$$

• According to  $i_C - i_E$  characteristics

$$i_E = \frac{i_C}{\alpha} = 2.02mA$$

• According to i - v characteristics of resistor

$$R_E = 7.07k\Omega$$

### **Recall: BJT in Saturation Mode**

$$\mathbf{i}_{C} = \left(\alpha_{F} - \frac{1}{\alpha_{R}}\right) I_{S} \left(e^{\frac{\mathbf{v}_{BC}}{V_{T}}} - 1\right) + \alpha_{F} i_{E}$$

When  $v_{BC}$  is increasing  $\rightarrow i_C$  decreases

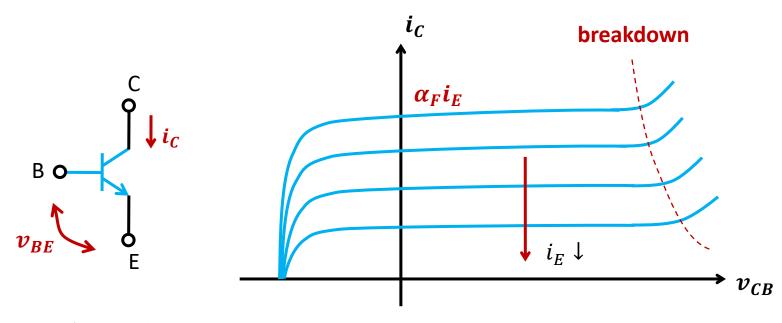

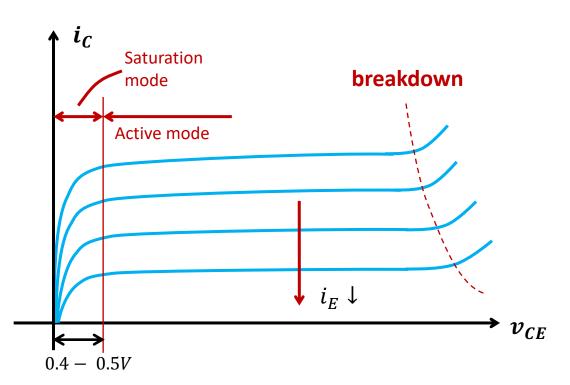

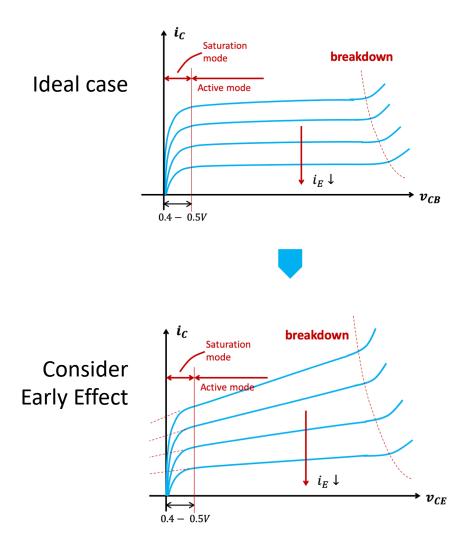

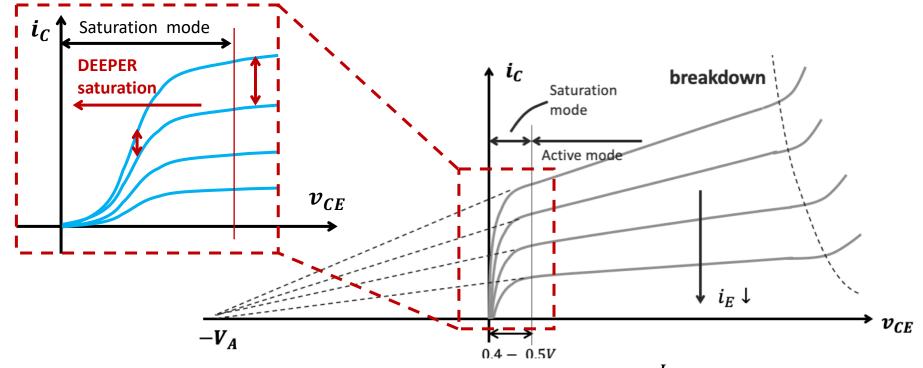

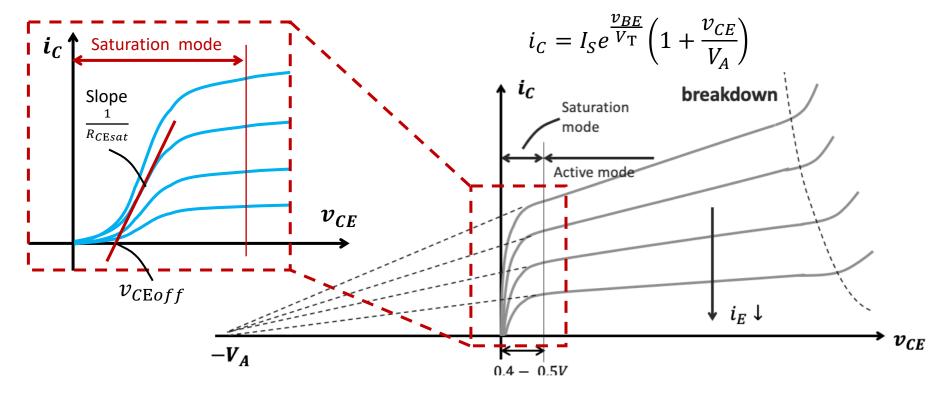

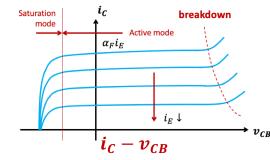

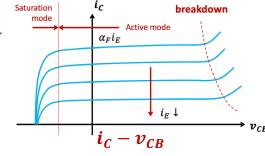

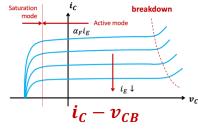

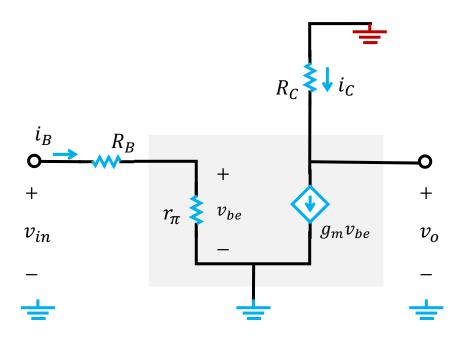

# $I_C - v_{CB}$ Characteristics

$$i_{C} = \left(\alpha_{F} - \frac{1}{\alpha_{P}}\right)I_{S}\left(e^{\frac{v_{BC}}{V_{T}}} - 1\right) + \alpha_{F}i_{E}$$

$i_{C} = \alpha_{F}i_{E}$  when  $v_{CB} = 0$

$$i_C = \alpha_F i_E$$

when

$$v_{CB} = 0$$

# $i_C - v_{CB}$ Characteristics

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Active mode

- Reverse mode

- Saturation mode

- □ npn v.s. pnp

v = i - v characteristics

breakdown

Active mode

$i_C - v_{CB}$

$i_E \downarrow$

$\alpha_F i_E$

reverse mode

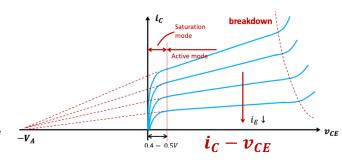

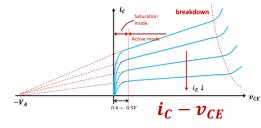

#### **Recall: A Model for Active Mode**

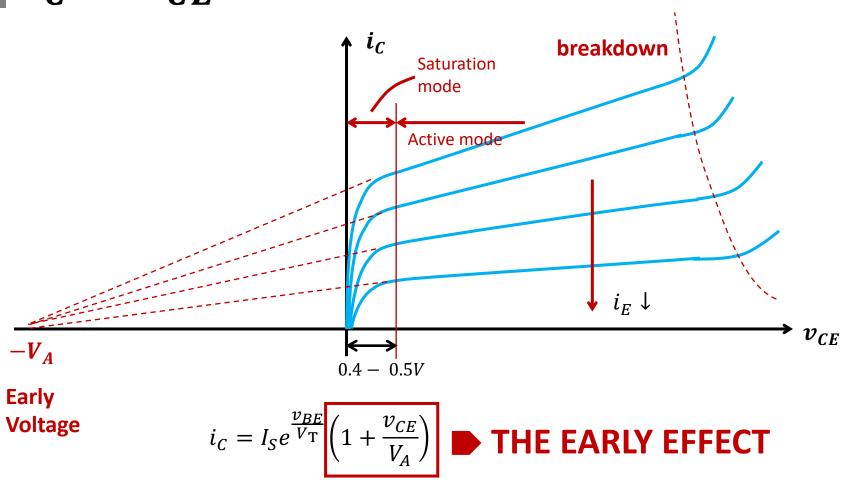

### **WHY the Early Effect**

$$i_C = I_S e^{\frac{v_{BE}}{V_T}}$$

where

$$I_S = \frac{A_E q D_n n_i^2}{N_A W}$$

$$v_{CE}$$

1

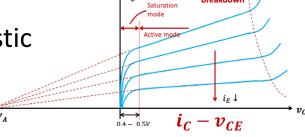

$$i_C = I_S e^{\frac{v_{BE}}{V_{\rm T}}} \left( 1 + \frac{v_{CE}}{V_A} \right)$$

$$r_o \equiv \left[ \frac{\partial i_C}{\partial v_{CE}} \right|_{v_{BE}} \right]^{-1}$$

$$= \frac{V_A + V_{CE}}{I_C} \approx \frac{V_A}{I_C}$$

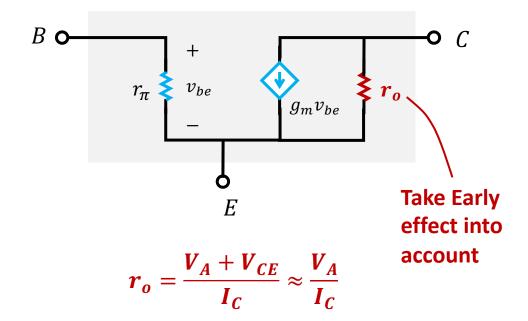

The nonzero slop of the  $i_{\it C}-v_{\it CE}$  characteristics straight lines indicates that the output resistance looking into the collector is NOT infinite.

- We already have  $\beta_{DC}$  for large signal, defined as  $\beta_{DC} = \frac{I_C}{I_B}$

- Define incremental  $\beta_{AC}$  as  $\left. \beta_{AC} = \frac{\Delta i_C}{\Delta i_B} \right|_{v_{CE}}$

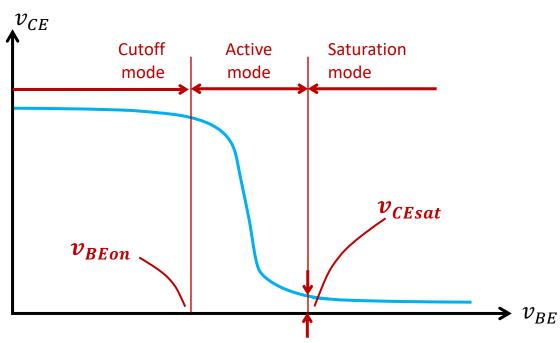

#### $\beta_{AC}$ is smaller in saturation mode than in active mode

The saturation voltage  $v_{CEsat} = v_{CEoff} + I_{Csat}R_{CEsat}$ Typical value 0.1 - 0.3V

Where

$$R_{CEsat}$$

is defined as  $R_{CEsat} \equiv \frac{\partial v_{CE}}{\partial i_C} \bigg|_{\substack{i_B = I_B \\ i_C = I_{Csat}}}$

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Active mode

- Reverse mode

- Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- $\neg i v$  characteristics

Active mode

reverse mode

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

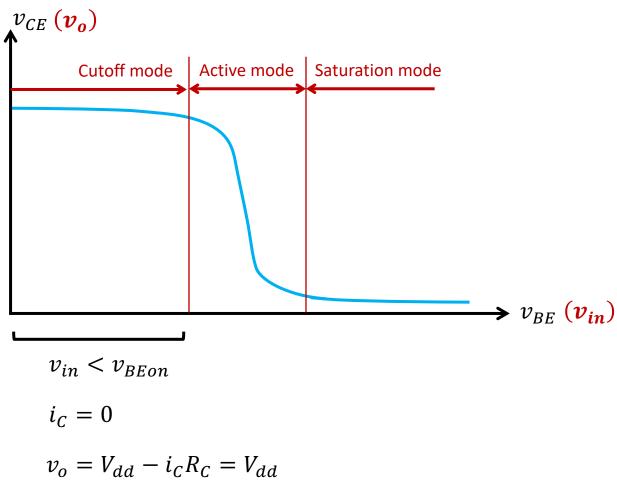

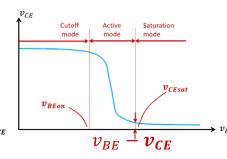

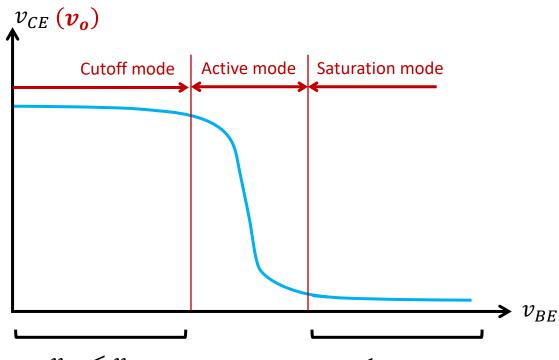

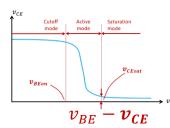

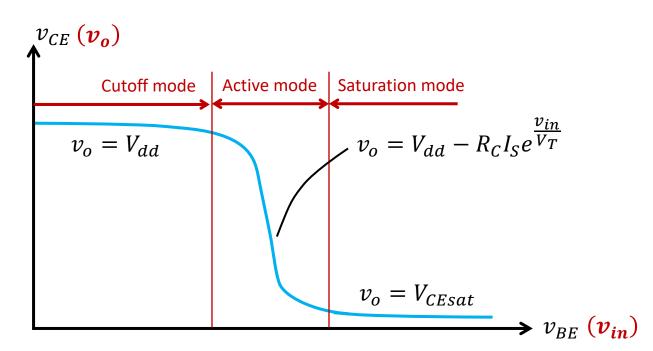

The transfer characteristic

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

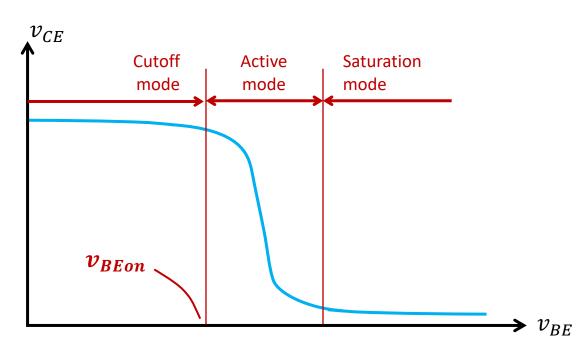

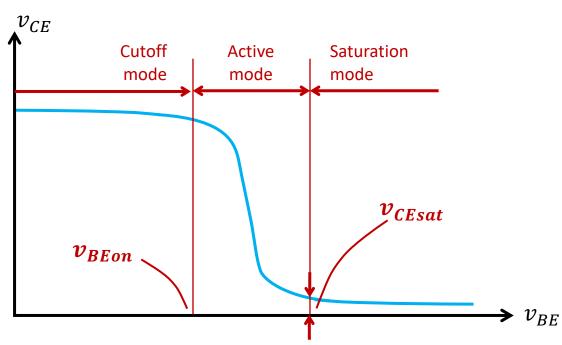

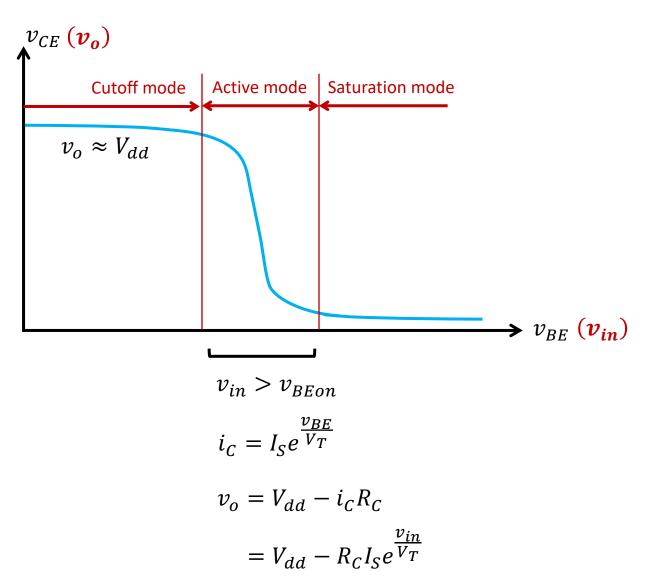

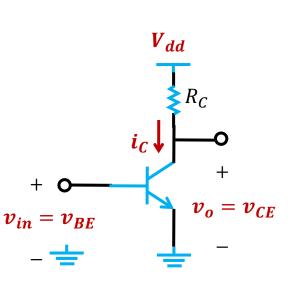

#### @ Cutoff mode

EBJ is off

$v_{BE} < v_{BEon}$

Typical value of  $v_{BEon}$  is 0.5V

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

#### @ Saturation mode

EBJ is on  $v_{BE} > v_{BEon}$

CBJ is on  $v_{BC} = v_{BE} - v_{CE} > v_{BCon}$

Typical value of  $v_{BCon}$  is 0.4V

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

#### @ Active mode

EBJ is on  $v_B$

CBJ is off

$$v_{BE} > v_{BEon}$$

$$v_{BC} = v_{BE} - v_{CE} < v_{BCon}$$

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Active mode

- Reverse mode

- Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

breakdown

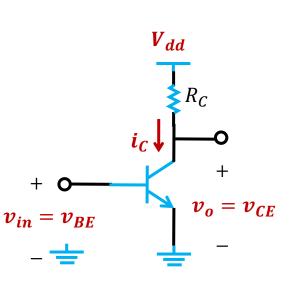

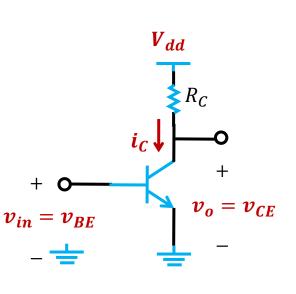

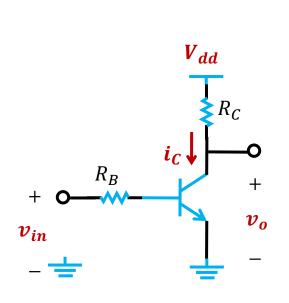

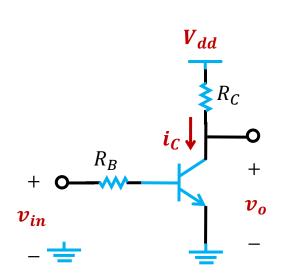

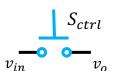

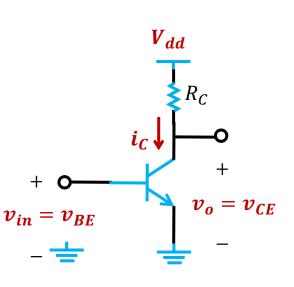

### Recall: Cutoff/Saturation Mode

$$v_{in} < v_{BEon}$$

$$i_C = 0$$

$$v_o = V_{dd} - i_C R_C = V_{dd}$$

$$v_o < v_{in} - v_{BCon}$$

$$v_{CE} = V_{CEsat}$$

$$I_{Csat} = \frac{V_{dd} - V_{CEsat}}{R_C}$$

### **Transistor in Cutoff/Saturation Mode**

Cutoff mode

Saturation mode

$$v_o = v_{in}$$

When  $S_{ctrl} = V_H$

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- Transistor in cutoff/saturation mode

- Transistor in active mode

#### Recall: Example 1

**QUESTION:** The transistor has  $\beta=100$  and exhibits a  $v_{BE}$  of 0.7V at  $i_C=1mA$ . Find the resistance of  $R_C$  and  $R_E$  when the transistor is biased in active region at  $i_C=2mA$  and  $v_{CB}=5V$  with  $V_C=V_E=15V$

$$V_C = i_C R_C + v_{CB} \qquad \rightarrow \quad R_C = 5k\Omega$$

Since

$$i_C = 1mA$$

@  $v_{BE} = 0.7V$

$$v_{BE}\Big|_{i_C=2mA} = 0.7 + V_T In\left(\frac{2mA}{1mA}\right) = 0.717V$$

$$V_E = i_E R_E + v_{BE} \qquad \rightarrow \quad i_E R_E = 15.717V$$

$$i_E = \frac{i_C}{\alpha} = 2.02 mA$$

where  $\alpha = \frac{\beta}{\beta + 1} = 0.99$

$$R_F = 7.07k\Omega$$

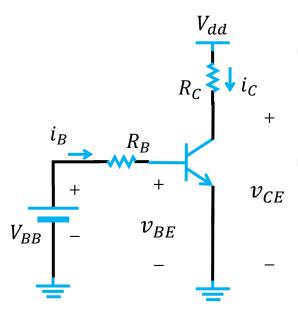

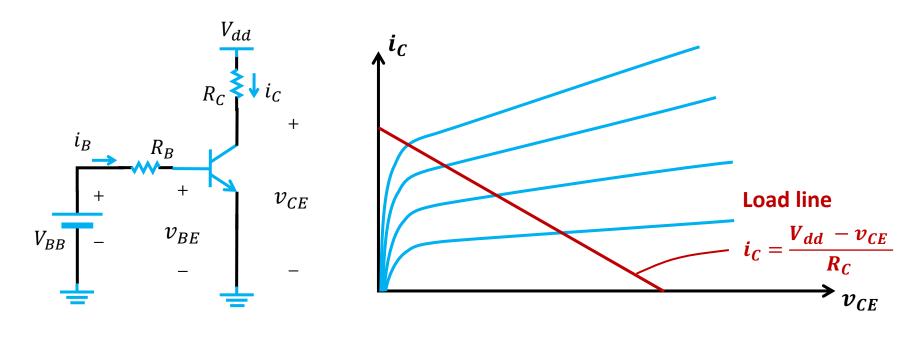

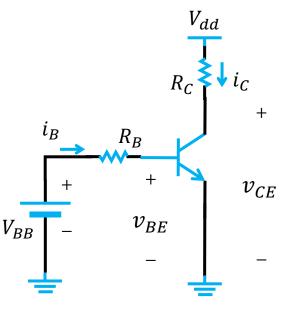

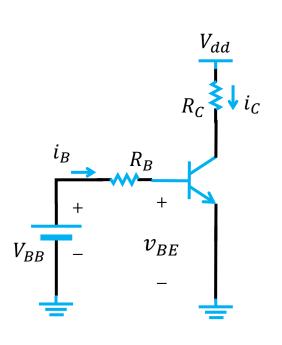

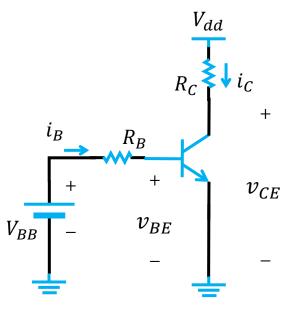

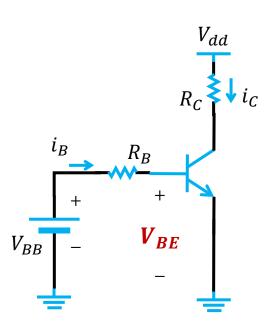

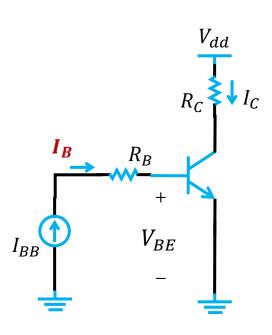

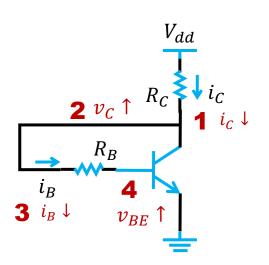

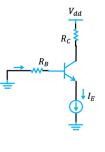

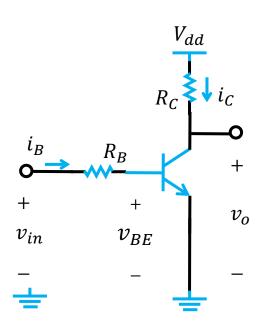

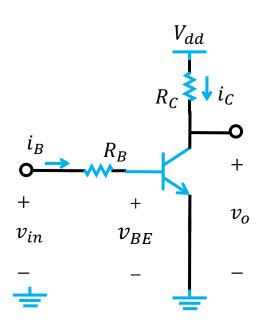

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_B=100k\Omega$ ,  $R_C=2k\Omega$ ,  $V_{dd}$ =10V,  $V_{BB}=5V$ , and  $\beta=100$ .

According to KVL

$$V_{BB} = i_B R_B + v_{BE}$$

• According to  $m{i}_{\it{C}} - m{v}_{\it{BE}}$  characteristics  $i_{\it{C}} = I_{\it{S}} e^{rac{m{v}_{\it{BE}}}{V_{\it{T}}}}$

$$V_E = \frac{I_S}{\beta} e^{\frac{\boldsymbol{v}_{BE}}{V_T}} R_B + \boldsymbol{v}_{BE}$$

1 unknown in 1 equation

BUT WE CANNOT FIND AN ANALYTICAL SOLUTION

NUMERICAL SOLUTION AVAILABLE IN 20230253

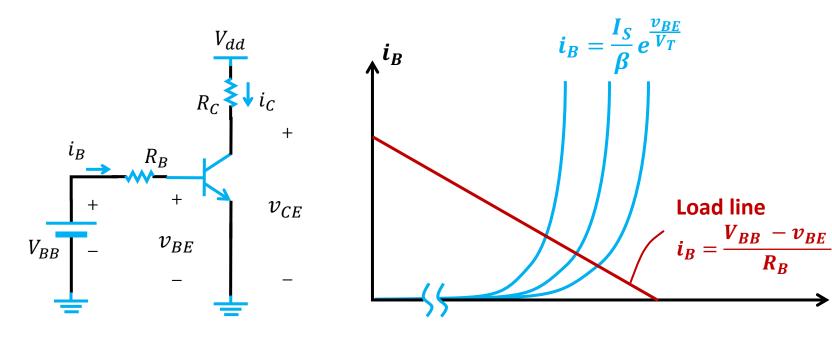

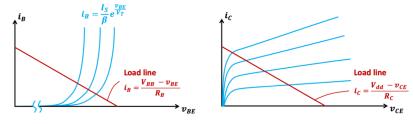

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_B=100k\Omega$ ,  $R_C=2k\Omega$ ,  $V_{dd}$ =10V,  $V_{BB}=5V$ , and  $\beta=100$ .

- According to KVL

- $V_{BB} = i_B R_B + v_{BE}$

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_B=100k\Omega$ ,  $R_C=2k\Omega$ ,  $V_{dd}$ =10V,  $V_{BB}=5V$ , and  $\beta=100$ .

# The graphical analysis tech is NOT quantitative.

Find the load line according to KVL

$$V_{dd} = i_C R_C + v_{CE}$$

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_B = 100k\Omega$ ,  $R_C = 2k\Omega$ ,  $V_{dd}$ =10V,  $V_{BB}=5V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0$ . 7V in active mode.

- Let's **ASSUME** the transistor is biased in active mode

- $\downarrow$   $i_C$  According to characteristics of the transistor +  $V_{BE} \approx 0.7V$

$$V_{BE} \approx 0.7V$$

According to KVL & transistor characteristics

$$\begin{cases} V_{BB} = i_B R_B + V_{BE} \\ V_{dd} = i_C R_C + V_{CE} \\ i_C = \beta i_B = 4.3 mA \end{cases} \qquad \begin{cases} i_B = 0.043 mA \\ i_C = 4.3 mA \\ V_{CE} = 1.4 V \end{cases}$$

#### **Check ASSUMPTION**

$$V_{BC} = -0.7V < V_{BCon}$$

**Active mode**

#### **Summary: DC analysis for BJT**

Method 1 – quantitative analysis

Method 2 – graphical analysis

- © Easy to operate

- **not a quantitative result**

- Method 3  $|V_{BE}| \approx V_{th} = 0.7V$  in active mode

- Step 1: assume the transistor is in active region

- Step 2: solve the circuit

- Step 3: check assumption

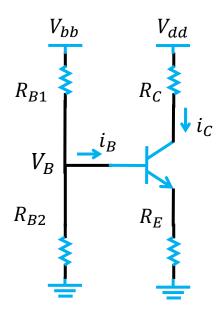

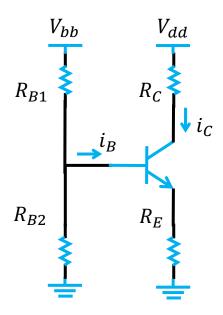

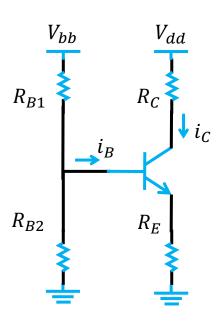

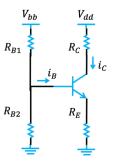

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_{B1}=100k\Omega$ ,  $R_{B2}=50k\Omega$ ,  $R_{C}=5k\Omega$ ,  $R_{E}=3k\Omega$ ,  $V_{dd}=V_{BB}=15V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

Assume the transistor is biased in active region

$$i_C = \beta i_B$$

$V_{BE} \approx V_{th} = 0.7V$

According to KVL & KCL

$$\begin{cases} \frac{V_{bb} - V_B}{R_{B1}} = \frac{V_B}{R_{B2}} + i_B \\ V_B = V_{BE} + (\beta + 1)i_B R_E \end{cases}$$

2 unknown in 2 equations

**ANY better way?**

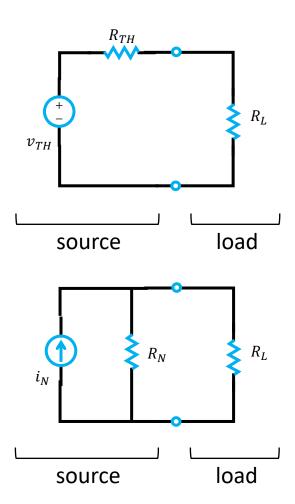

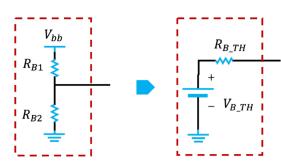

#### Recall: Circuit equivalent

#### Thévenin's theorem

LINEAR two-terminal circuit can be replaced by an equivalent circuit composed of a voltage source and a series resistor

#### Norton's theorem

LINEAR two-terminal circuit can be replaced by an equivalent circuit composed of a current source and a parallel resistor

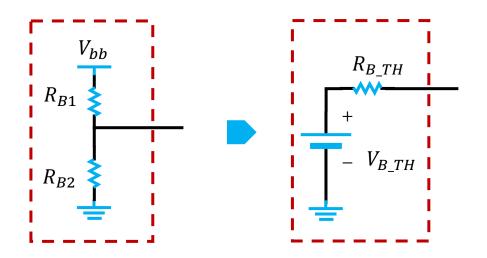

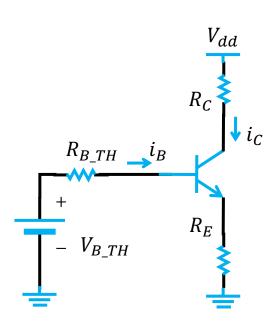

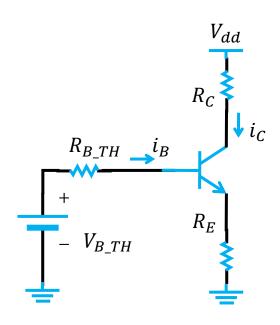

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_{B1}=100k\Omega$ ,  $R_{B2}=50k\Omega$ ,  $R_{C}=5k\Omega$ ,  $R_{E}=3k\Omega$ ,  $V_{dd}=V_{BB}=15V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

According to Thévenin's theorem

$$R_{B\_TH} = R_{B1} || R_{B2} = 33.3k\Omega$$

$$V_{B\_TH} = \frac{R_{B2}}{R_{B1} + R_{B2}} V_{dd} = 5V$$

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_{B1}=100k\Omega$ ,  $R_{B2}=50k\Omega$ ,  $R_{C}=5k\Omega$ ,  $R_{E}=3k\Omega$ ,  $V_{dd}=V_{BB}=15V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

$$\begin{cases} R_{B\_TH} = 33.3k\Omega \\ V_{B\_TH} = 5V \end{cases}$$

Assume the transistor is biased in active region

$$i_C = \beta i_B$$

$V_{BE} \approx V_{th} = 0.7V$

According to KVL & KCL

$$\begin{cases} V_{B\_TH} = i_B R_{B\_TH} + V_{BE} + i_E R_E \\ V_C = V_{dd} - i_C R_C \\ i_E = i_B + i_C = (\beta + 1) i_B \end{cases}$$

$$\begin{cases} i_B = 0.0128mA \\ V_C = 8.6V \\ V_E = i_E R_E = 3.88V \end{cases}$$

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_{B1}=100k\Omega$ ,  $R_{B2}=50k\Omega$ ,  $R_{C}=5k\Omega$ ,  $R_{E}=3k\Omega$ ,  $V_{dd}=V_{BB}=15V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

$$\begin{cases} R_{B\_TH} = 33.3k\Omega \\ V_{B\_TH} = 5V \end{cases}$$

• The voltage of  $V_{BE}$  and  $V_{CE}$  can be calculated as

$$V_{BE} = V_{B\_TH} - i_B R_{B_{TH}} - V_E = 0.694V$$

$V_{CE} = V_{dd} - i_C R_C - V_E = -3.664V$

#### Check ASSUMPTION

$$V_{BE} = 0.694V$$

$> V_{BEon}$

$V_{BC} = -3.664V$   $< V_{BCon}$

#### **Active mode**

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_{B1}=100k\Omega$ ,  $R_{B2}=50k\Omega$ ,  $R_{C}=5k\Omega$ ,  $R_{E}=3k\Omega$ ,  $V_{dd}=V_{BB}=15V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

$$\begin{cases} R_{B\_TH} = 33.3k\Omega \\ V_{B\_TH} = 5V \end{cases}$$

#### The ASSUMPTION

$$i_C = \beta i_B$$

$$V_{BE} \approx V_{th} = 0.7V$$

#### **DC** analysis results

$$V_{BC} = 0.05 \text{ fV}$$

$V_{BC} = -3.664 \text{ V}$

#### WHY the voltage of $V_{RE}$ is different?

A more precise method

$$V_{B\_TH} = \frac{I_S}{\beta} e^{\frac{v_{BE}}{V_T}} R_{B\_TH} + V_{BE} + \frac{I_S}{\beta} e^{\frac{v_{BE}}{V_T}} R_E$$

1 unknown in 1 equation

#### **BUT WE CANNOT FIND AN ANALYTICAL SOLUTION**

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

| Mode           | EBJ     | СВЈ     |

|----------------|---------|---------|

| Cutoff         | Reverse | Reverse |

| Active         | Forward | Reverse |

| Saturation     | Forward | Forward |

| Reverse Active | Reverse | Forward |

- Method 1 quantitative analysis

- Method 2 graphical analysis

- Method 3  $|V_{BE}| \approx V_{th} = 0.7V$  in active mode

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- AC analysis techniques

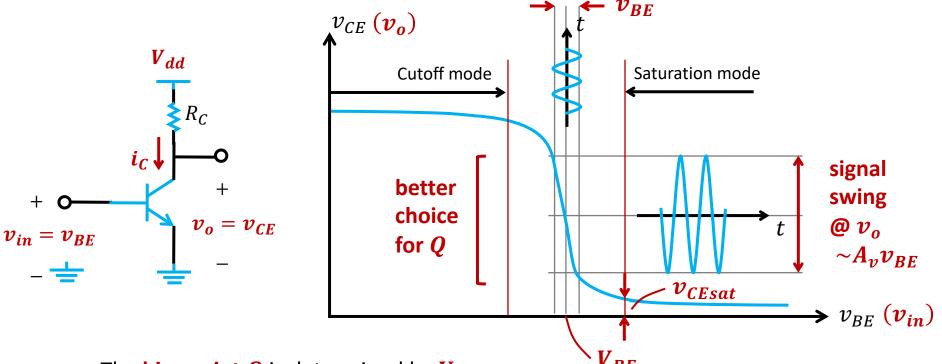

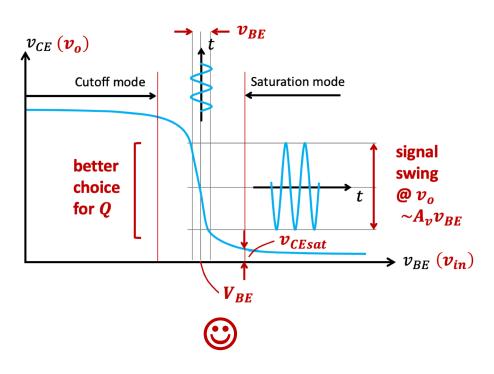

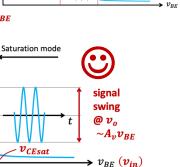

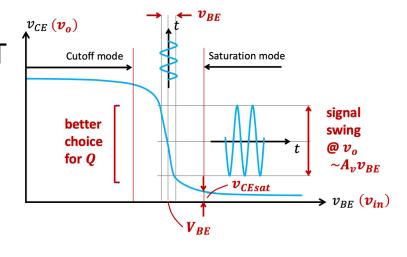

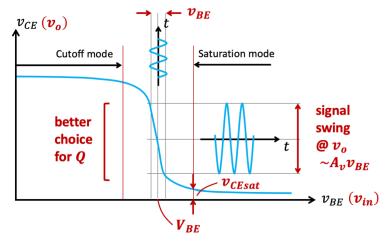

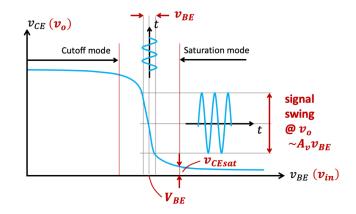

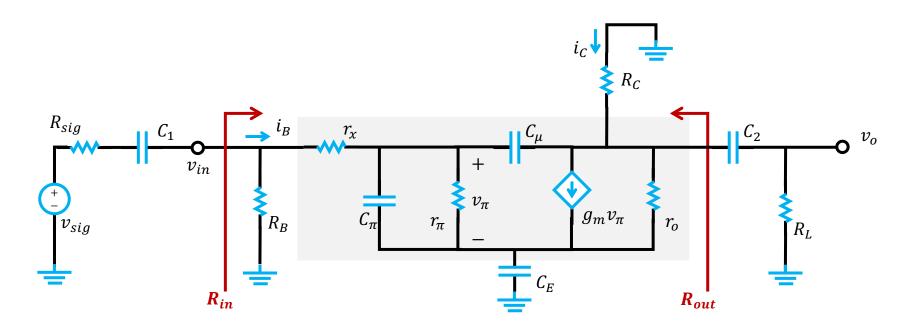

#### **Recall: the Transfer Characteristic**

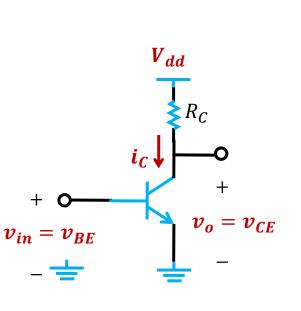

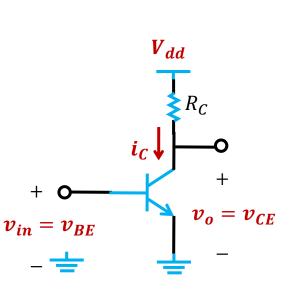

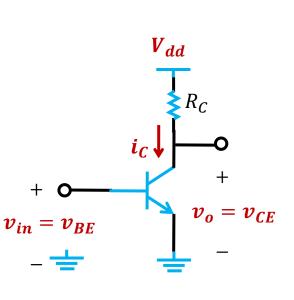

### **Signal Amplification**

- Step 1 find a proper bias point / quiescent point

- Step 2 characterized by DC voltages  $V_{BE}$  and  $V_{CE}$

$$V_{CE} = V_{dd} - R_C I_S e^{\frac{V_{BE}}{V_T}}$$

• Step 3 a sufficiently small voltage  $v_{BE}$  superimposed on  $V_{BE}$

# **Signal Amplification**

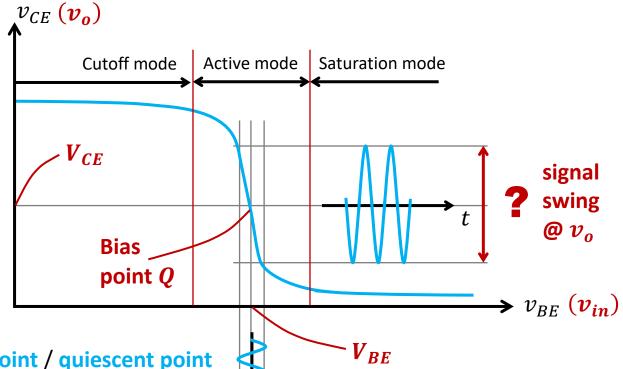

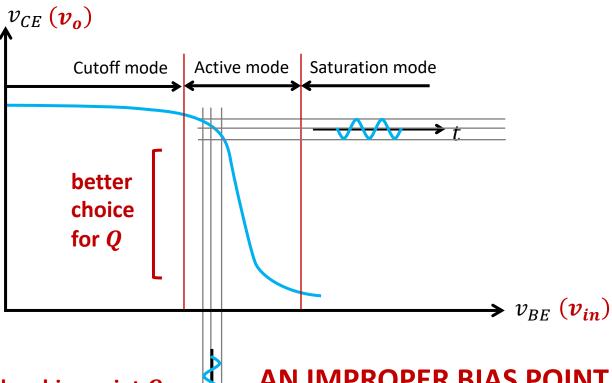

# **Locating the Bias Point**

#### CASE 1

- BJT is biased @ relative low bias point Q

- A sufficiently small AC amplitude is applied

AN IMPROPER BIAS POINT MAY CAUSE A TOO LOW SMALL SIGNAL VOLTAGE GAIN

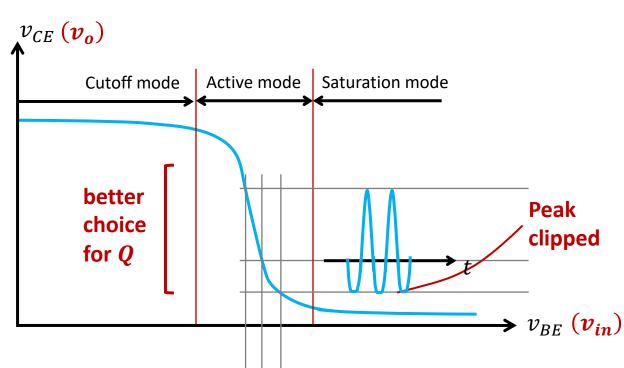

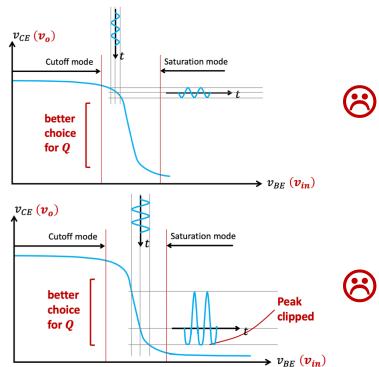

# **Locating the Bias Point**

#### CASE 2

- BJT is biased @ a fine quiescent point

- A larger AC amplitude is applied

- The peak of the output is clipped

A NOT SMALL ENOUGH AC INPUT MAY CAUSE A DISASTER TO LINEARITY PERFORMANCE

# **Locating the Bias Point**

- The bias point Q is determined by  $V_{BE}$

- The GAIN  $A_v$  is determined by the location of Q

- The allowable SIGNAL SWING at the output must be considered

#### LOCATING THE BIAS POINT IS IMPORTANT IN SMALL SIGNAL AMPLIFICATION

#### ? How to locate the bias point

### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- AC analysis techniques

- Locating the bias point is important

- HOW to locate the bias point

### Recall: Example 2

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_B = 100k\Omega$ ,  $R_C = 2k\Omega$ ,  $V_{dd}$ =10V,  $V_{BB}=5V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

- Let's **ASSUME** the transistor is biased in **active mode**

$$V_{BE} \approx 0.7V$$

$$\begin{cases} V_{BB} = i_B R_B + V_{BE} \\ V_{dd} = i_C R_C + V_{CE} \\ i_C = \beta i_B = 4.3 mA \end{cases} \qquad \begin{cases} i_B = 0.043 mA \\ i_C = 4.3 mA \\ V_{CE} = 1.4 V \end{cases}$$

#### **Check ASSUMPTION**

$$V_{BC} = -0.7V < V_{BCon}$$

**Active mode**

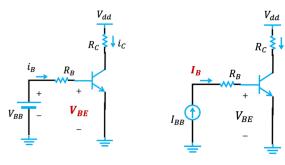

■ Method 1 – Locate the bias point by fixing  $V_{BE}$

$I_C$  is **too sensitive** to the change of  $V_{BE}$

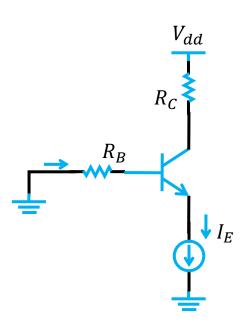

Method 2 – Locate the bias point by fixing I<sub>B</sub>

According transistor characteristics, in active mode

$$I_C = \beta I_B$$

The large variations of  $\beta$  results in large variation in  $I_C$

■ Method 3 – Using Constant-Current Source

- $I_E$  is independent of  $\beta$  and  $R_B$

- How to realize a current source?

- Current mirror explained in next chapter

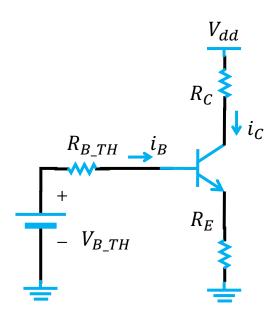

### Recall: Example 3

**QUESTION:** Find out the voltage of  $V_{BE}$  and  $V_{CE}$  with  $R_{B1}=100k\Omega$ ,  $R_{B2}=50k\Omega$ ,  $R_{C}=5k\Omega$ ,  $R_{E}=3k\Omega$ ,  $V_{dd}=V_{BB}=15V$ , and  $\beta=100$ . Assume  $|V_{BE}|=0.7V$  in active mode.

According to Thévenin's theorem

$$R_{B\_TH} = R_{B1} || R_{B2} = 33.3k\Omega$$

$$V_{B\_TH} = \frac{R_{B2}}{R_{B1} + R_{B2}} V_{dd} = 5V$$

- Assume the transistor is biased in active region

- The voltage of  $V_{BE}$  and  $V_{CE}$  can be calculated as

$$V_{BE} = V_{B\_TH} - i_B R_{B_{TH}} - V_E = 0.694V$$

$V_{CE} = V_{dd} - i_C R_C - V_E = -3.664V$

Check assumption

According to KVL & Thévenin's theorem

$$I_E = \frac{V_{B\_TH} - V_{BE}}{R_E + R_B/(\beta + 1)}$$

where  $V_{B\_TH} = \frac{R_{B2}}{R_{B1} + R_{B2}} V_{dd}$

• Since

$$V_{B\_TH} \gg V_{BE}$$

,  $R_E \gg \frac{R_B}{\beta + 1}$

A better tolerance to the variation of  $V_{BE}$

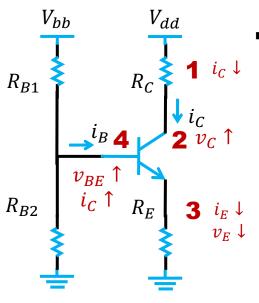

Method 4 – Classical Discrete-Circuit Arrangement

• What is  $R_E$  used for?

- $\circ$  If there is a decrease @  $i_C$

- $\circ$  The voltage drop on  $R_C$  decreases

- $\circ$   $i_E$  and  $v_E$  decrease correspondingly

- $\circ$   $v_{BE}$  increases, causing an increasing of  $i_{\mathcal{C}}$

**NEGATIVE FEEDBACK is observed**

$R_E$  stabilizes the bias current

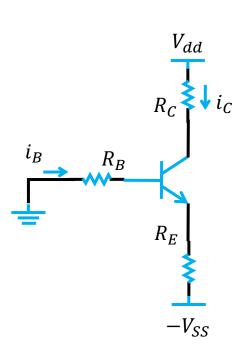

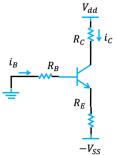

Method 5 – Two-Power-Supply Version

According to KVL & transistor characteristics

$$V_{SS} = I_B R_B + V_{BE} + I_E R_E$$

$$I_E = (\beta + 1)I_B$$

if the transistor is in active mode

$$i_E = \frac{V_{SS} - V_{BE}}{R_E + R_B / (\beta + 1)}$$

According to KVL & transistor characteristics

$$V_{dd} = I_C R_C + I_B R_B + V_{BE}$$

$$I_E = (\beta + 1)I_B$$

if the transistor is in active mode

$$i_E = \frac{V_{dd} - V_{BE}}{R_C + R_B/(\beta + 1)}$$

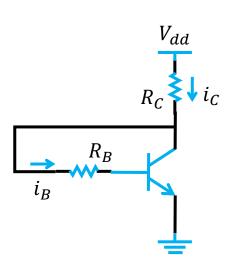

Method 6 – Collector-to-Base Feedback Resistor

• What is  $R_B$  used for?

- $\circ$  If there is a decrease @  $i_C$

- $\circ$  The voltage drop on  $R_C$  decreases,  $v_C$  increases

- $\circ$   $i_B$  decrease correspondingly

- $\circ$   $v_{BE}$  increases, causing an increasing of  $i_C$

**NEGATIVE FEEDBACK is observed**

$R_B$  stabilizes the bias point

# **Summary: Locate the Bias Point**

#### **WHY?** Key to small signal amplification

- Q is determined by  $V_{BE}$

- Q determines the **GAIN**  $A_v$

- Q has effects on the OUTPUT SIGNAL SWING

# **Summary: Locate the Bias Point**

#### WHY?

#### Key to small signal amplification

- Q is determined by  $oldsymbol{V_{BE}}$

- Q determines the GAIN  $A_v$

- Q has effects on the OUTPUT SIGNAL SWING

#### HOW?

fixing  $I_R$

fixing  $I_E$

Cutoff mode

better

choice

$v_{CE}\left(\boldsymbol{v_o}\right)$

Cutoff mode

better

choice

for Q

Classical Discrete-Circuit Arrangement

Two-Power-Supply Version

Cutoff mode

choice for Q

Collector-to-Base Feedback Resistor

### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- AC analysis techniques

- Locate the bias point

- Small-signal operation & model

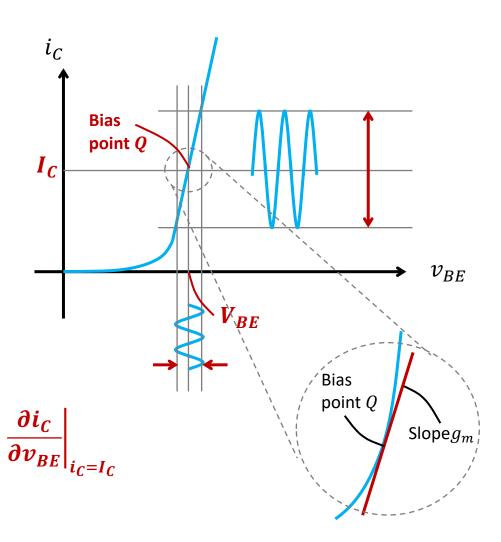

# **Small-Signal Operation**

- The transistor is biased @  $v_{be} = v_{BE}$

- A small AC signal is applied to input

### **Small-Signal Operation**

$$v_{in} = V_{BE} + v_{be} sin(\omega t + \varphi) = V_{BE} + v_{in,AC}$$

According to the transistor characteristic

$$i_{C} = I_{S}e^{\frac{v_{BE}}{V_{T}}} = I_{S}e^{\frac{v_{BE}+v_{in,AC}}{V_{T}}} = I_{S}e^{\frac{v_{in,AC}}{V_{T}}}e^{\frac{v_{in,AC}}{V_{T}}}$$

$$= I_{C}e^{\frac{v_{in,AC}}{V_{T}}}$$

$$= I_{C}e^{\frac{v_{in,AC}}{V_{T}}}$$

$$| \mathbf{f} v_{in,AC} \ll V_{T} |$$

$$\approx I_{C}\left(1 + \frac{v_{in,AC}}{V_{T}}\right)$$

$$i_{C} = I_{C} + \frac{I_{C}}{V_{T}} v_{in,AC} = I_{C} + g_{m} v_{in,AC}$$

$$Define$$

$$i_{C}@DC$$

$$i_{C}@AC$$

TRANSCONDUCTANCE  $g_{m} = \frac{I_{C}}{V_{T}}$

# Transconductance $g_m$

$$v_{in} = V_{BE} + v_{in,AC}$$

$$i_C = I_C + g_m v_{in,AC}$$

TRANSCONDUCTANCE

$$\left. g_m = \frac{\partial i_C}{\partial v_{BE}} \right|_{i_C = I_C}$$

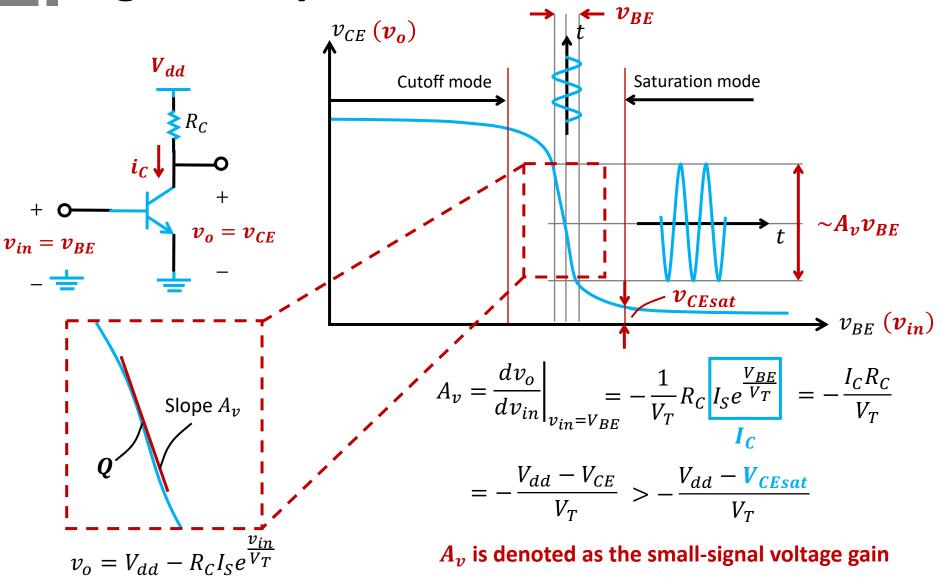

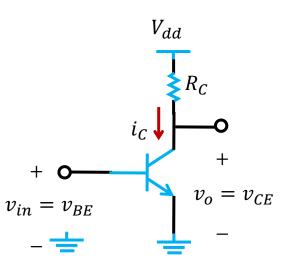

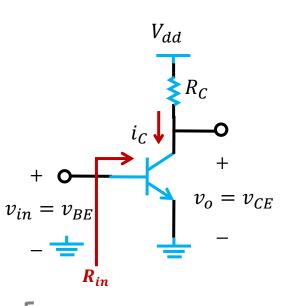

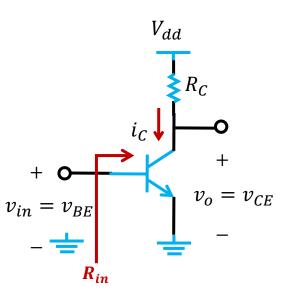

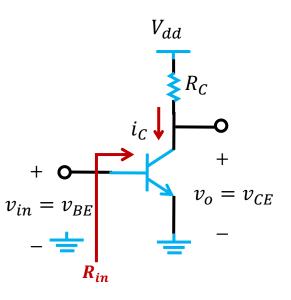

# Voltage Gain $A_v$

$$v_{in} = V_{BE} + v_{AC}$$

$$i_C = I_C + g_m v_{AC}$$

$$g_m = \frac{\partial i_C}{\partial v_{BE}} \Big|_{i_C = I_C} = \frac{I_C}{V_T}$$

According to KVL

$$v_{o} = V_{dd} - i_{C}R_{C} = V_{dd} - \left(i_{C}\Big|_{DC} + i_{C}\Big|_{AC}\right)R_{C}$$

$$= V_{dd} - I_{C}R_{C} - i_{C}\Big|_{AC}R_{C}$$

$$V_{CE} \qquad g_{m}v_{AC}$$

Define voltage gain

$$A_v = \frac{v_o|_{AC}}{v_{in}|_{AC}} = \frac{-g_m v_{AC} R_C}{v_{AC}} = -g_m R_C$$

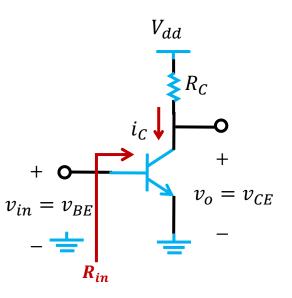

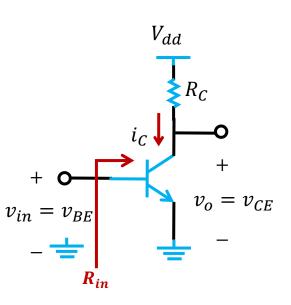

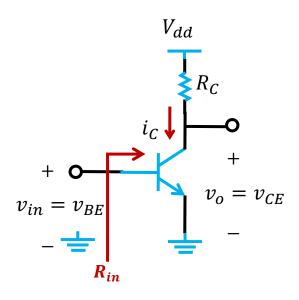

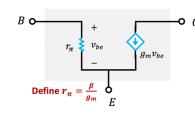

# Input Resistance @ Base

$$v_{in} = V_{BE} + v_{AC}$$

$$i_C = I_C + g_m v_{AC}$$

• According to the definition of  $R_{in}$

$$R_{in} = \frac{\Delta v_{in}}{\Delta i_{in}} = \frac{\Delta v_{BE}}{\Delta i_{B}}$$

According to the transistor characteristic in active mode

$$i_B = \frac{i_C}{\beta} = \frac{I_C}{\beta} + \frac{1}{\beta} \frac{I_C}{V_T} v_{AC}$$

$$\Delta i_B = \frac{1}{\beta} \frac{I_C}{V_T} v_{AC} = \frac{1}{\beta} g_m v_{AC}$$

Thus,

nus,

$$R_{in} = \frac{\Delta v_{BE}}{\Delta i_B} = \frac{v_{AC}}{\Delta i_B} = \frac{V_T}{I_B} \quad \text{or} \quad = \frac{\beta}{g_m}$$

# **Summary: Small-Signal Operation**

$$v_{in} = V_{BE} + v_{be}sin(\omega t + \varphi) = V_{BE} + v_{AC}$$

Voltage gain

$$A_v = \frac{v_o|_{AC}}{v_{in}|_{AC}} = -g_m R_C$$

Transconductance

$$g_m = \frac{\partial i_C}{\partial v_{BE}}\Big|_{i_C = I_C} = \frac{I_C}{V_T}$$

Input resistance @ Base

$$R_{in} = \frac{V_T}{I_B} = \frac{\beta}{g_m}$$

$$v_{in} = V_{BE} + v_{be} sin(\omega t + \varphi) = V_{BE} + v_{AC}$$

$$\text{Voltage gain} \quad A_v = \frac{v_o|_{AC}}{v_{in}|_{AC}} = -g_m R_C$$

$$\text{Transconductance} \quad g_m = \frac{\partial i_C}{\partial v_{BE}} \bigg|_{i_C = I_C} = \frac{I_C}{V_T}$$

$$\text{Input resistance @ Base} \quad R_{in} = \frac{V_T}{I_B} = \frac{\beta}{g_m}$$

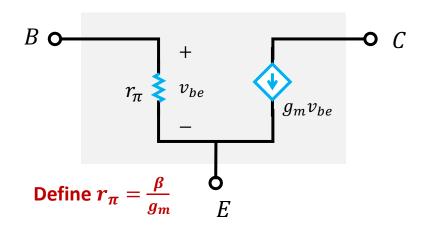

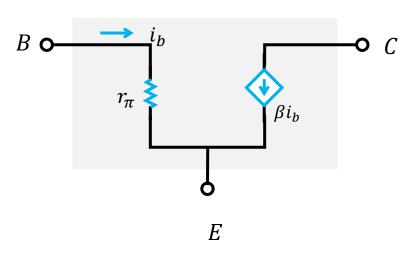

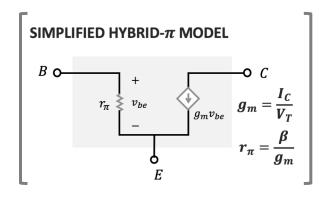

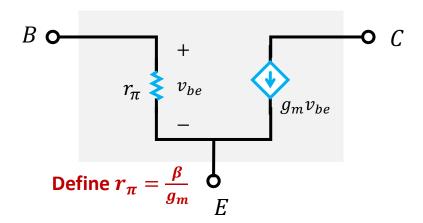

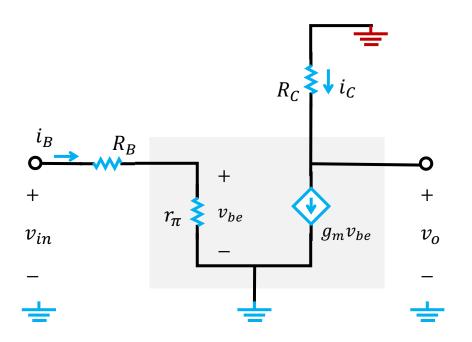

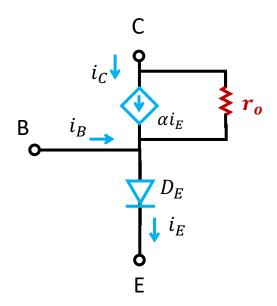

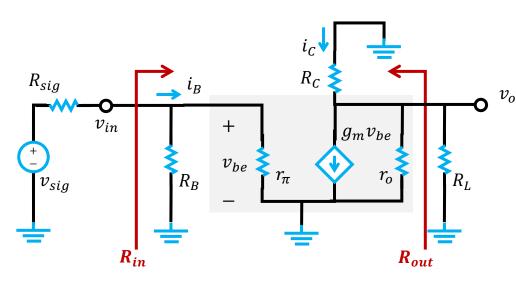

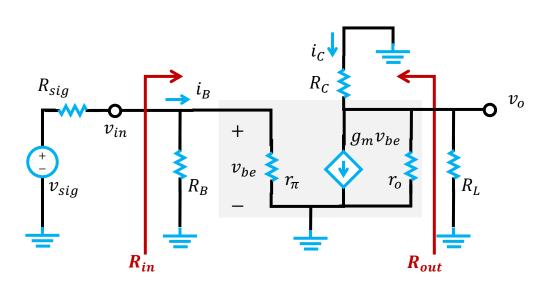

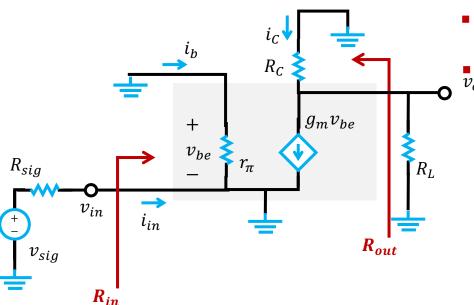

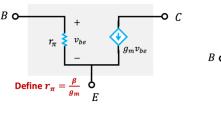

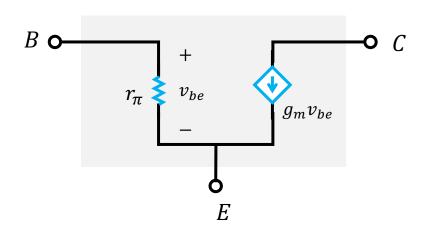

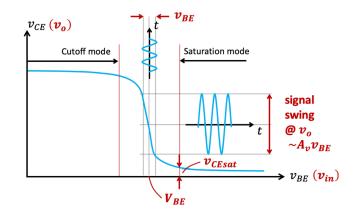

#### SIMPLIFIED HYBRID- $\pi$ MODEL

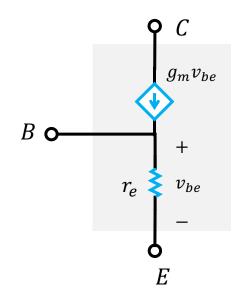

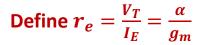

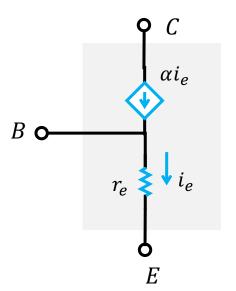

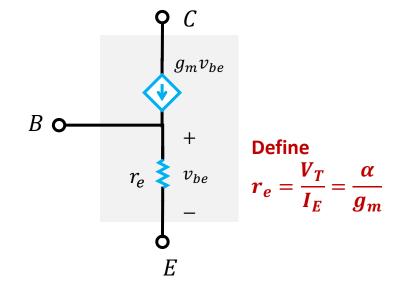

#### SIMPLIFIED T MODEL

#### SIMPLIFIED HYBRID- $\pi$ MODEL

- According to hybrid- $\pi$  model

- $i_b = \frac{v_{be}}{r_{\pi}}$

#### SIMPLIFIED T MODEL

#### According to T model

$$i_b = \frac{v_{be}}{r_e} - g_m v_{be} = \frac{v_{be}}{r_e} (1 - g_m r_e) = \frac{v_{be}}{r_e} (1 - \alpha) = \frac{v_{be}}{(1 + \beta)r_e} = \frac{v_{be}}{r_{\pi}}$$

#### HYBRID- $\pi$ MODEL and T MODEL are equivalent

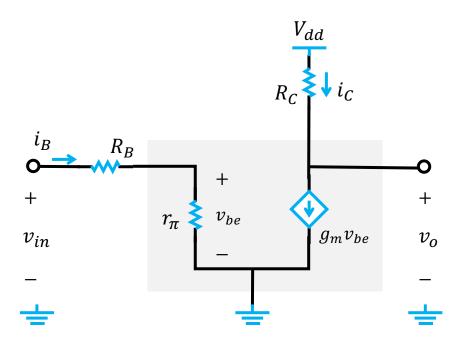

**QUESTION:** Find out the voltage of  $v_o$  with  $v_{in}=3V+0.1sin(\omega t+\varphi)$ ,  $R_B=100k\Omega$ ,  $R_C=3k\Omega$ ,  $V_{dd}=10V$ , and  $\beta=100$ . The threshold voltage  $V_{th}=0.7V$ .

#### Step 1: perform DC analysis

- Let's ASSUME the transistor is biased in active mode

- According to KVL & transistor characteristics

$$\begin{cases} v_{in} \Big|_{DC} = i_B R_B + V_{th} \\ V_C = V_{dd} - i_C R_C \\ i_C = \beta i_B \end{cases} \qquad \begin{cases} i_B = 0.023 mA \\ V_C = 3.1 V \end{cases}$$

#### Check ASSUMPTION

$$V_{BE} = 0.7V$$

$> V_{BEon}$

$V_{BC} = -2.4V$   $< V_{BCon}$

**Active mode**

**QUESTION:** Find out the voltage of  $v_o$  with  $v_{in}=3V+0.1sin(\omega t+\varphi)$ ,  $R_B=100k\Omega$ ,  $R_C=3k\Omega$ ,  $V_{dd}=10V$ , and  $\beta=100$ . The threshold voltage  $V_{th}=0.7V$ .

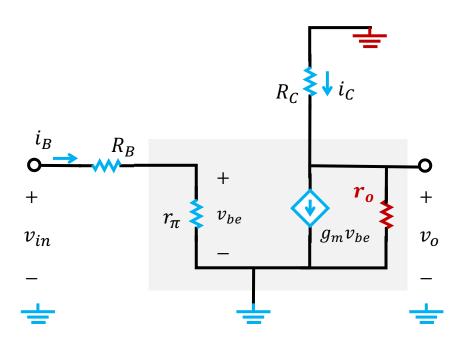

#### Step 2: perform AC analysis

Step 2.1: replace the transistor with the small-signal model

**QUESTION:** Find out the voltage of  $v_o$  with  $v_{in}=3V+0.1sin(\omega t+\varphi)$ ,  $R_B=100k\Omega$ ,  $R_C=3k\Omega$ ,  $V_{dd}=10V$ , and  $\beta=100$ . The threshold voltage  $V_{th}=0.7V$ .

#### Step 2: perform AC analysis

- Step 2.1: replace the transistor with the small-signal model

- Step 2.2: turn off DC sources

- SHORT all voltage sources

- OPEN all current sources

- Step 2.3: Calculate small-signal model parameters

$$g_m = \frac{I_C}{V_T} = \frac{2.3mA}{25mV} = 92mA/V$$

$$r_{\pi} = \frac{\beta}{g_m} = 1.086k\Omega$$

**QUESTION:** Find out the voltage of  $v_o$  with  $v_{in}=3V+0.1sin(\omega t+\varphi)$ ,  $R_B=100k\Omega$ ,  $R_C=3k\Omega$ ,  $V_{dd}=10V$ , and  $\beta=100$ . The threshold voltage  $V_{th}=0.7V$ .

#### Step 2: perform AC analysis

Step 2.4: Analyze resulting circuit

$$v_o = -g_m v_{be} R_C$$

$$= -g_m R_C \frac{r_{\pi}}{R_B + r_{\pi}} v_{in}$$

The voltage gain

$$A_v = \frac{v_o}{v_{in}} = -g_m R_C \frac{r_\pi}{R_B + r_\pi}$$

$$= -3.04$$

# **Recall: the Early Effect**

$$r_o = \frac{V_A + V_{CE}}{I_C} \approx \frac{V_A}{I_C}$$

#### SIMPLIFIED HYBRID- $\pi$ MODEL

**QUESTION:** Find out the voltage of  $v_o$  with  $v_{in}=3V+0.1sin(\omega t+\varphi)$ ,  $R_B=100k\Omega$ ,  $R_C=3k\Omega$ ,  $V_{dd}=10V$ , and  $\beta=100$ ,  $V_A=100V$ . The threshold voltage  $V_{th}=0.7V$ .

#### Step 2: perform AC analysis

Step 2.4: Analyze resulting circuit

$$v_o = -g_m v_{be}(R_C || r_o)$$

$$= -g_m(R_C || r_o) \frac{r_\pi}{R_B + r_\pi} v_{in}$$

The voltage gain

$$A_v = \frac{v_o}{v_{in}} = -g_m(R_C||r_o)\frac{r_\pi}{R_B + r_\pi}$$

### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- AC analysis techniques

- Locate the bias point

- Small-signal operation & model

- Characterizing Amplifiers

#### SIMPLIFIED HYBRID- $\pi$ MODEL

# $r_{\pi} \geqslant v_{be} \qquad g_{m}v_{be}$ Define $r_{\pi} = \frac{\beta}{g_{m}}$

#### SIMPLIFIED T MODEL

### Recall: Example 4

**QUESTION:** Find out the voltage of  $v_o$  with  $v_{in}=3V+0.1sin(\omega t+\varphi)$ ,  $R_B=100k\Omega$ ,  $R_C=3k\Omega$ ,  $V_{dd}=10V$ , and  $\beta=100$ . The threshold voltage  $V_{th}=0.7V$ .

Step 1: perform DC analysis

$$V_{BE} = 0.7V$$

$> V_{BEon}$  Active mode  $V_{BC} = -2.4V$

Step 2: perform AC analysis

$$v_{o} = -g_{m}v_{be}R_{c} = -g_{m}R_{c}\frac{r_{\pi}}{R_{B} + r_{\pi}}v_{in}$$

$$A_{v} = \frac{v_{o}}{v_{in}} = -g_{m}R_{c}\frac{r_{\pi}}{R_{B} + r_{\pi}} = -3.04$$

The AC amplitude of  $v_{in}$  is amplified

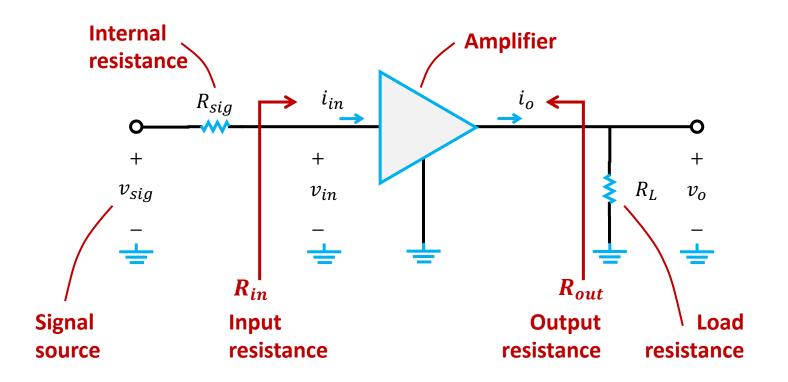

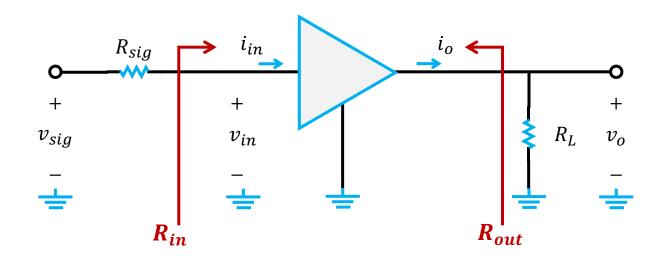

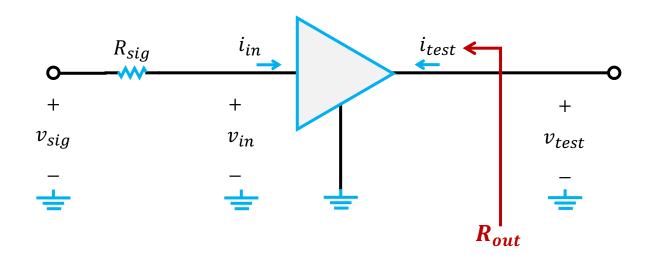

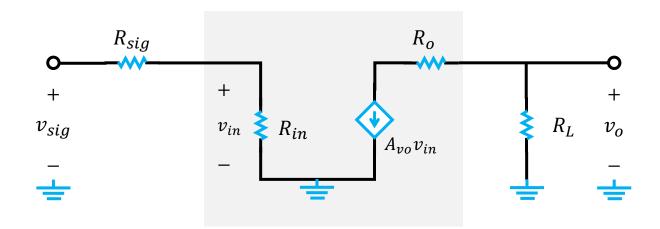

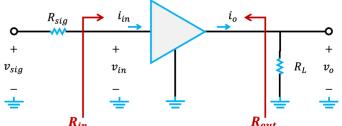

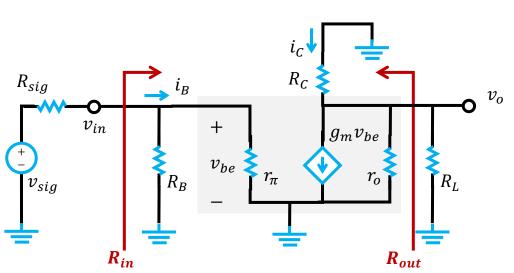

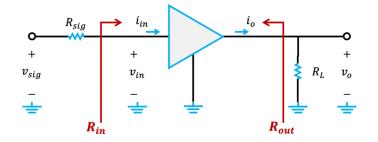

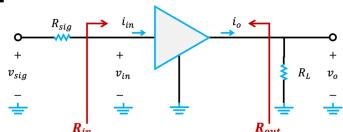

**Define OPEN-CIRCUIT VOLTAGE GAIN**

$$A_{vo} \equiv \frac{v_o}{v_{in}}\bigg|_{R_L = \infty}$$

Define INPUT RESISTANCE  $R_{in} \equiv \frac{v_{in}}{i}$

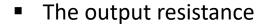

How to calculate OUTPUT RESISTANCE  $R_{out}$

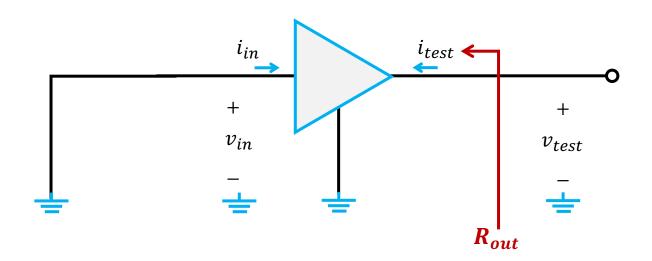

#### How to calculate OUTPUT RESISTANCE $R_{out}$

Step 1: remove load and apply a testing voltage

#### How to calculate OUTPUT RESISTANCE $R_{out}$

- Step 1: remove load and apply a testing voltage

- Step 2: turn off the input source

- SHORT all voltage sources

- OPEN all current sources

- Step 3: calculate the output resistance  $R_{out} = \frac{v_{test}}{i_{test}}$

• According to KVL

$$v_o = \frac{R_L}{R_L + R_o} A_{vo} v_{in}$$

- Define the voltage gain of the amplifier  $A_v \equiv \frac{v_o}{v_{in}} = \frac{R_L}{R_L + R_o} A_{vo}$

- Define the overall voltage gain  $G_v \equiv \frac{v_o}{v_{sig}} = \frac{R_{in}}{R_{in} + R_{sig}} \frac{R_L}{R_L + R_o} A_{vo}$

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- AC analysis techniques

- Locate the bias point

- Small-signal operation & model

- Characterizing Amplifiers

- Basic BJT Amplifier Configurations

# SIMPLIFIED HYBRID- $\pi$ MODEL $B \circ C$ $r_{\pi} \stackrel{\downarrow}{\downarrow} v_{be}$ $Define <math>r_{\pi} = \frac{\beta}{g_{m}} \circ E$ SIMPLIFIED T MODEL $F_{g_{m}v_{be}} \circ C$ $F_{e} \stackrel{\downarrow}{\downarrow} v_{be}$ $F_{e} \stackrel{\downarrow}{\downarrow} v_{be}$ $F_{e} \stackrel{\downarrow}{\downarrow} v_{be}$ $F_{e} \stackrel{\downarrow}{\downarrow} v_{be}$ $F_{e} \stackrel{\downarrow}{\downarrow} v_{be}$

- Assume the transistor is biased in active mode

- There are three ports: Base, Collector and Emitter

- An amplifier requires two voltages:  $v_{in}$  and  $v_{o}$

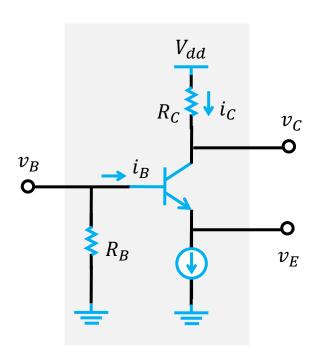

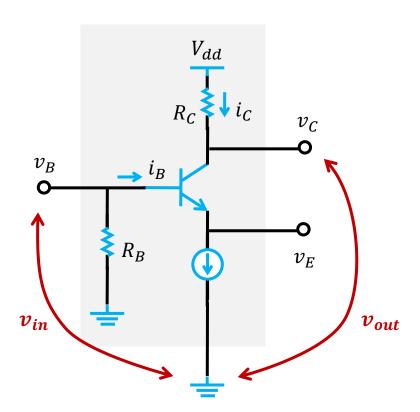

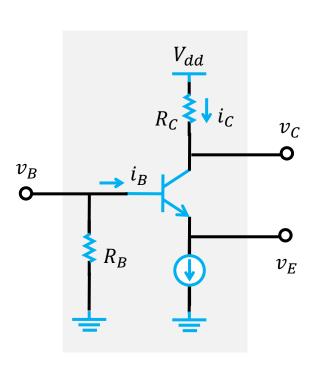

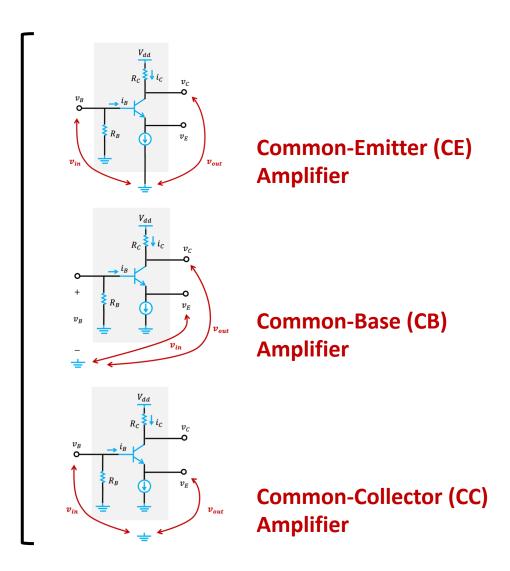

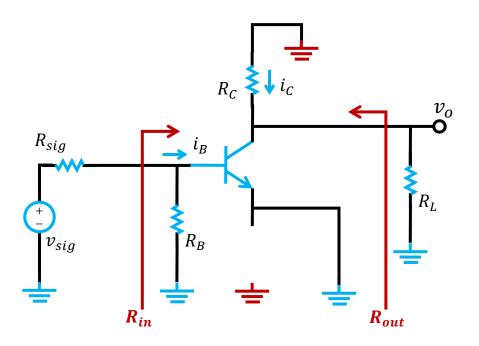

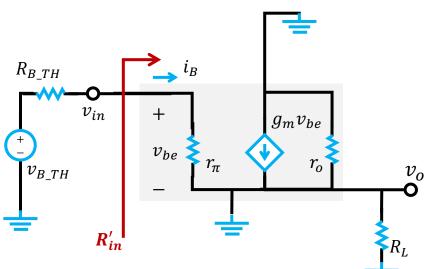

#### **Common-Emitter (CE) Amplifier**

• The Emitter is "shared" by  $v_{in}$  and  $v_o$

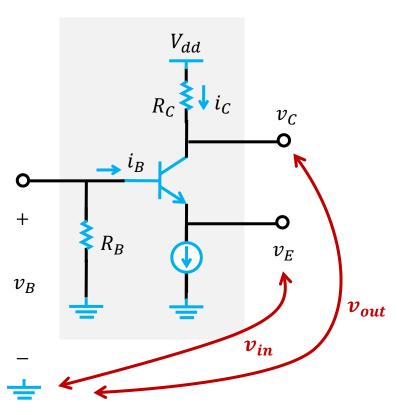

#### **Common-Base (CB) Amplifier**

lacktriangle The Base is "shared" by  $v_{in}$  and  $v_o$

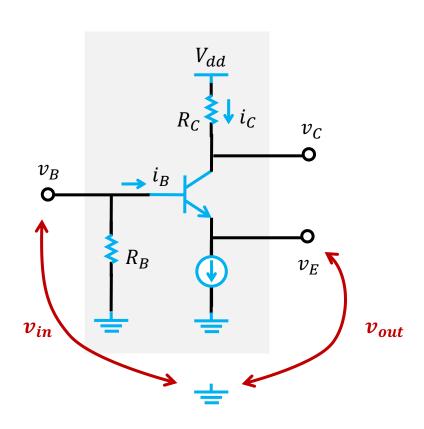

#### **Common-Collector (CC) Amplifier**

• The Collector is "shared" by  $v_{in}$  and  $v_o$

- Assume the transistor is biased in active mode

- There are three ports: Base,

Collector and Emitter

- An amplifier requires two voltages:  $v_{in}$  and  $v_{o}$

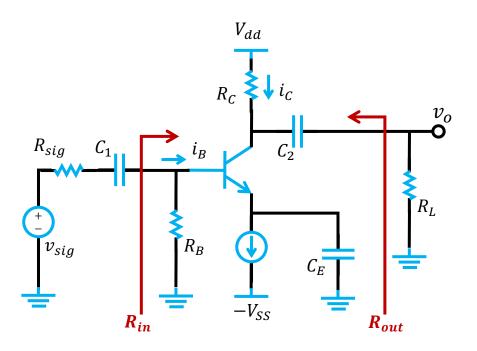

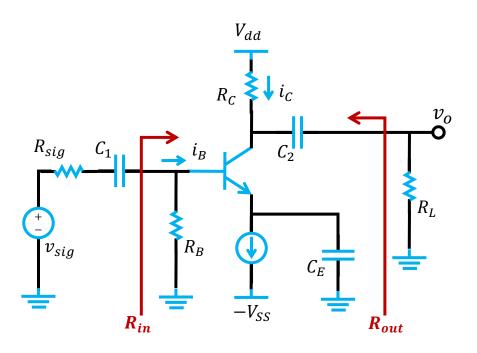

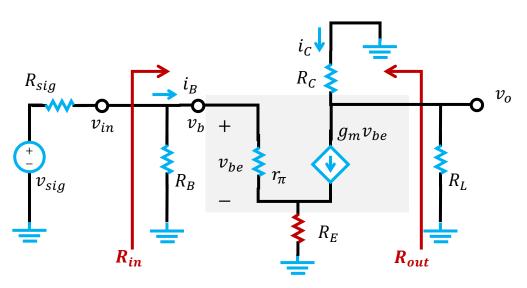

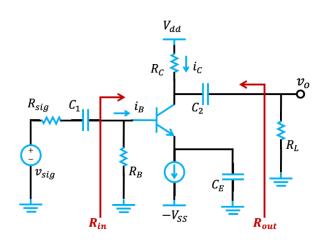

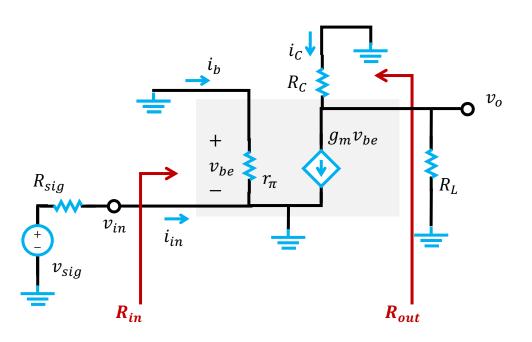

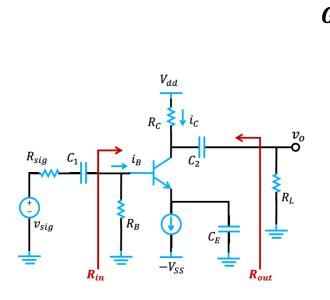

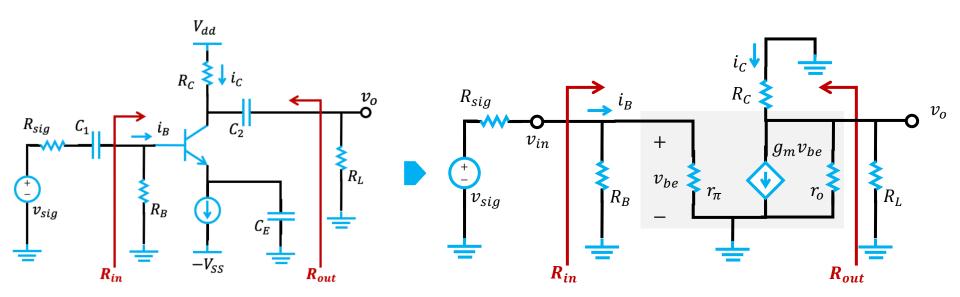

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

#### Step 1: perform DC analysis

- Step 1.1: ASSUME the transistor is biased in active mode

- Step 1.2: calculate all the DC currents and voltages according to KVL/KCL

- Step 1.3: Check ASSUMPTION

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

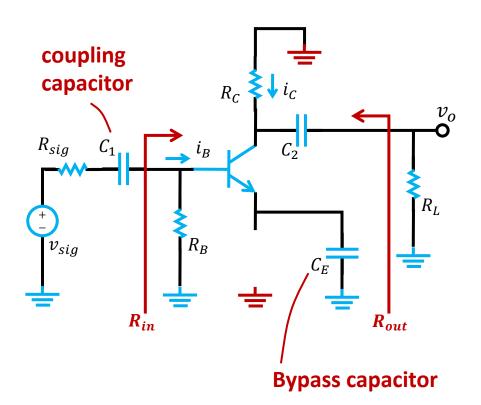

#### Step 2: perform AC analysis

- Step 2.1: turn off DC sources

- SHORT all voltage sources

- OPEN all current sources

$$Z_{C_E} = \frac{1}{sC_E}$$

The bypass capacitor  $C_E$  provides a very LOW impedance to ground at all signal frequencies of interest

The coupling capacitor  $\mathcal{C}_1$  and  $\mathcal{C}_2$  act as perfect short circuit at all signal frequencies of interest

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

#### Step 2: perform AC analysis

- Step 2.1: turn off DC sources

- SHORT all voltage sources

- OPEN all current sources

The capacitors can APPROXIMATELY be as short circuit @ AC

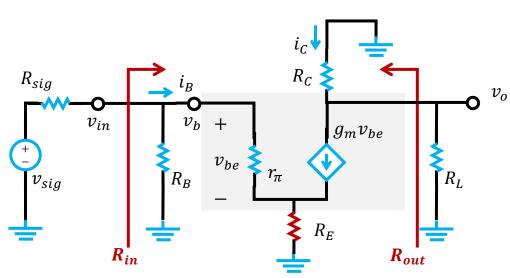

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

#### Step 2: perform AC analysis

- Step 2.1: turn off DC sources

- SHORT all voltage sources

- OPEN all current sources

- Step 2.2: Calculate small-signal model parameters,  $\beta$  and  $r_{\pi}$

- Step 2.3: replace the transistor with the small-signal model

- Step 2.4: Analyze the resulting circuit

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

According to KVL

$$v_{in} = v_{be} = \frac{R_B || r_{\pi}}{R_{sig} + R_B || r_{\pi}} v_{sig}$$

$v_o = -g_m v_{be} (R_C || R_L || r_o)$

The overall voltage gain

$$G_{v} = \frac{v_{o}}{v_{sig}}$$

$$= -\frac{R_{B}||r_{\pi}}{R_{sig} + R_{B}||r_{\pi}} g_{m}(R_{C}||R_{L}||r_{o})$$

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

■ Calculate the open-circuit voltage gain @  $R_L = \infty$

$$A_{vo} = \frac{v_o}{v_{in}} = -g_m(R_C||r_o)$$

Since

$$R_C \ll r_o \rightarrow A_{vo} \approx -g_m R_C$$

The input resistance

$$R_{in} = R_B || r_\pi \approx r_\pi$$

Since  $R_B \gg r_\pi$

The output resistance

$$R_{out} = R_C || r_o \approx R_C$$

Since  $r_o \gg R_C$

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

The VOLTAGE GAIN is relative high

$$G_v = \frac{v_o}{v_{sig}} = -\frac{R_B||r_{\pi}}{R_{sig} + R_B||r_{\pi}} g_m(R_C||R_L||r_o)$$

$$A_{vo} = \frac{v_o}{v_{in}} = -g_m(R_C||r_o)$$

The INPUT RESISTANCE is relative low

$$R_{in} = R_B || r_{\pi} \approx r_{\pi}$$

The OUTPUT RESISTANCE is relative high

$$R_{out} = R_C || r_o \approx R_C$$

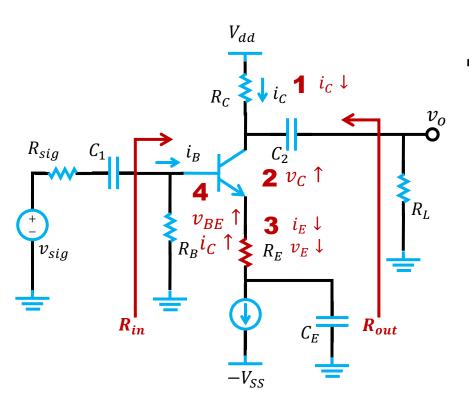

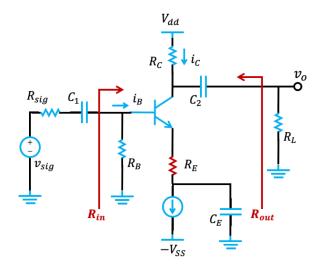

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $R_E$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

- What is  $R_E$  used for?

- $\circ$  If there is a decrease @  $i_C$

- $\circ$   $v_C$  increases due to  $R_C$

- $\circ$   $i_E$  and  $v_E$  decrease correspondingly

- $\circ$   $v_{BE}$  increases, and  $i_{\mathcal{C}}$  increases

**NEGATIVE FEEDBACK is observed**

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $R_E$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

- Step 1: perform DC analysis (SKIP)

- Step 2: perform AC analysis

- Step 2.1: turn off DC sources (SKIP)

- Step 2.2: Calculate small-signal model parameters,  $\beta$  and  $r_{\pi}$  (SKIP)

- Step 2.3: replace the transistor with the small-signal model (SKIP)

- Step 2.4: Analyze the resulting circuit

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $R_E$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

According to KVL

$$v_{in} = (i_B + g_m r_\pi i_B) R_E + r_\pi i_B$$

$$v_{out} = -\beta i_B (R_C || R_L)$$

The input resistance

$$R_{in} = R_B || \frac{cest}{i_{test}}$$

$$= R_B || ((1 + g_m r_\pi) R_E + r_\pi)$$

Since  $R_B \gg r_\pi$

$$\approx (1 + g_m r_\pi) R_E + r_\pi$$

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $R_E$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

The overall voltage gain

$$G_{v} = \frac{v_{out}}{v_{sig}} = \frac{v_{b}}{v_{sig}} \frac{v_{out}}{v_{b}}$$

$$= -\frac{R_{in}}{R_{sig} + R_{in}} \frac{g_{m}r_{\pi}(R_{C}||R_{L})}{(1 + g_{m}r_{\pi})R_{E} + r_{\pi}}$$

$$\downarrow \text{Since } R_{in} \approx (1 + g_{m}r_{\pi})R_{E} + r_{\pi}$$

$$\approx -\frac{g_{m}r_{\pi}(R_{C}||R_{L})}{R_{r_{m}} + (1 + g_{m}r_{\pi})R_{r_{m}} + r_{\pi}}$$

|          | CE w/o emitter res.                                       | CE w/ emitter res.                                                                   |

|----------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|

| $R_{in}$ | $r_{\pi}$                                                 | $(1+g_mr_\pi)R_E+r_\pi \qquad \uparrow$                                              |

| $G_{v}$  | $-\frac{R_B  r_{\pi}}{R_{sig}+R_B  r_{\pi}}g_m(R_C  R_L)$ | $-\frac{g_m r_{\pi}(R_C  R_L)}{R_{sig} + (1 + g_m r_{\pi})R_E + r_{\pi}} \downarrow$ |

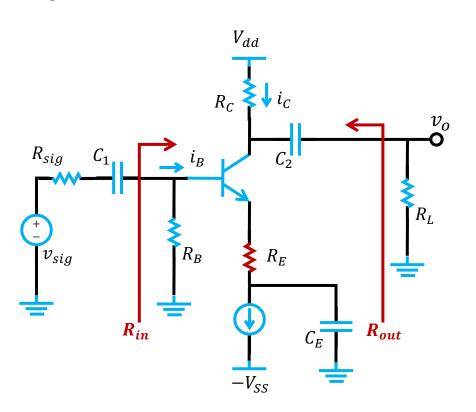

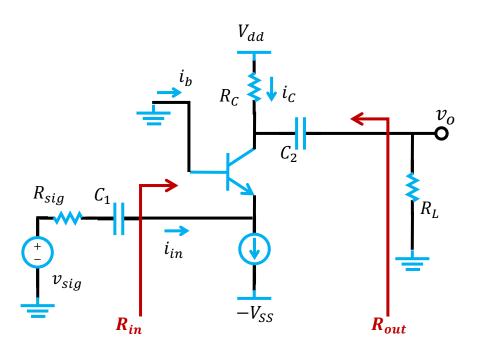

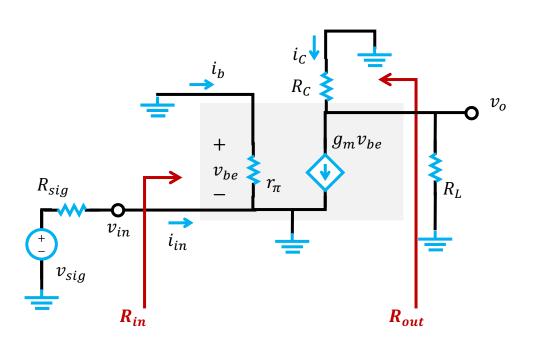

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

Step 1: perform DC analysis (SKIP)

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

- Step 1: perform DC analysis (SKIP)

- $v_o$  Step 2: perform AC analysis

- Step 2.1: turn off DC sources (SKIP)

- step 2.2: Calculate small-signal model parameters, β and  $r_π$  (SKIP)

- Step 2.3: replace the transistor with the small-signal model (SKIP)

- Step 2.4: Analyze the resulting circuit

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

According to KVL

$$v_{out} = -g_m v_{be}(R_C || R_L)$$

$$v_{in} = -v_{be} = \frac{R_{in}}{R_{sig} + R_{in}} v_{sig}$$

The input resistance

$$R_{in} = \frac{v_{test}}{i_{test}} = \frac{v_{in}}{i_{in}}$$

$$=\frac{-\iota_b r_\pi}{-\iota_b - g_m \iota_b r_\pi} = \frac{r_\pi}{1+\beta}$$

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ . Ignore the Early effect.

■ The overall voltage gain

$$G_v = \frac{v_{out}}{v_{sig}} = \frac{v_{in}}{v_{sig}} \frac{v_{out}}{v_{in}}$$

$$= \frac{R_{in}}{R_{sig} + R_{in}} g_m(R_C || R_L)$$

$$= \frac{1}{R_{sig} \frac{1+\beta}{\beta} + \frac{1}{g_m}} (R_C || R_L)$$

$$\approx \frac{1}{R_{sig} + \frac{1}{g_m}} (R_C || R_L)$$

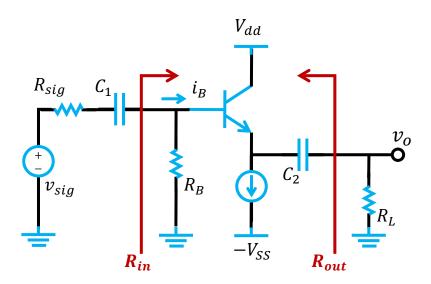

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

Step 1: perform DC analysis (SKIP)

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

- Step 1: perform DC analysis (SKIP)

- Step 2: perform AC analysis

- Step 2.1: turn off DC sources (SKIP)

- step 2.2: Calculate small-signal model parameters, β and  $r_π$  (SKIP)

- Step 2.3: replace the transistor with the small-signal model (SKIP)

- Step 2.4: Analyze the resulting circuit

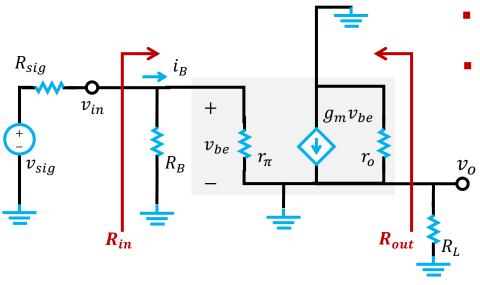

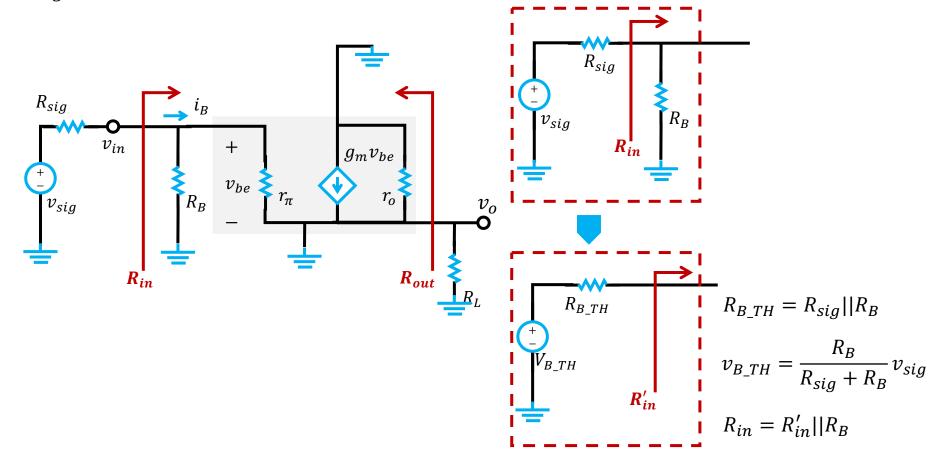

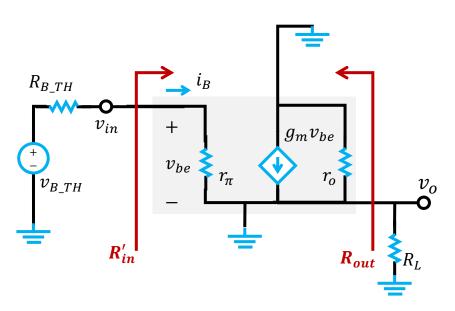

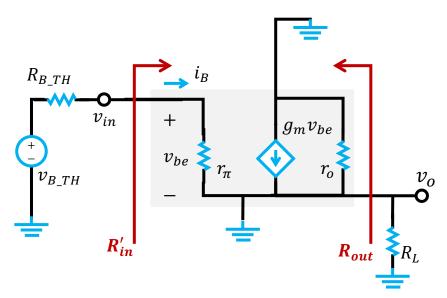

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,

$R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

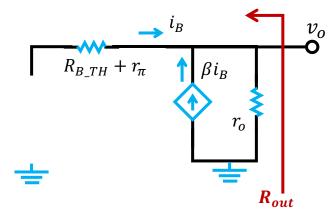

The input resistance

$$R_{in} = R'_{in}||R_B = \frac{v_{be}}{i_b}||R_B$$

$$= \frac{i_B r_\pi + (i_B + g_m i_B r_\pi)(r_o||R_L)}{i_B}||R_B$$

$$= [r_\pi + (1 + \beta)(r_o||R_L)]||R_B$$

$$R_{B\_TH} = R_{sig} || R_B$$

$v_{B\_TH} = \frac{R_B}{R_{sig} + R_B} v_{sig}$

$$R_{in} = R'_{in} || R_B$$

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

$$R_{B\_TH} = R_{sig}||R_B$$

$$v_{B\_TH} = \frac{R_B}{R_{sig} + R_B} v_{sig}$$

$$R_{in} = R'_{in} || R_B$$

$$R_{out} = r_o || \frac{R_{TH} + r_{\pi}}{1 + \beta} \approx \frac{R_{TH} + r_{\pi}}{1 + \beta}$$

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

The CC amplifier is also called EMITTER FOLLOWER

The output voltage

$$v_{o} = i_{B}(R'_{in} - r_{\pi}) = \frac{v_{B_{TH}}}{R_{B_{TH}} + R'_{in}} (R'_{in} - r_{\pi})$$

$$= \frac{R_{B}}{R_{sig} + R_{B}} \frac{(1 + \beta)(r_{o}||R_{L})}{R_{sig}||R_{B} + R'_{in}} v_{sig}$$

The overall gain

$$G_{v} = \frac{v_{o}}{v_{sig}} = \frac{R_{B}}{R_{sig} + R_{B}} \frac{(1+\beta)(r_{o}||R_{L})}{R_{sig}||R_{B} + R'_{in}} v_{sig}$$

$$\downarrow \text{If } R_{B} \gg R_{sig}, R_{in} \gg R_{sig}||R_{B}$$

$$\approx 1$$

# **Summary: 3 BJT Amp. Configurations**

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work?

- Cutoff / Active / Reverse / Saturation mode

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- Circuit analysis techniques with BJT

- DC analysis techniques

- AC analysis techniques

- Locate the bias point

- Small-signal operation & model

- Characterizing Amplifiers

- Basic BJT Amplifier Configurations

- The frequency response

#### SIMPLIFIED HYBRID- $\pi$ MODEL

#### SIMPLIFIED T MODEL

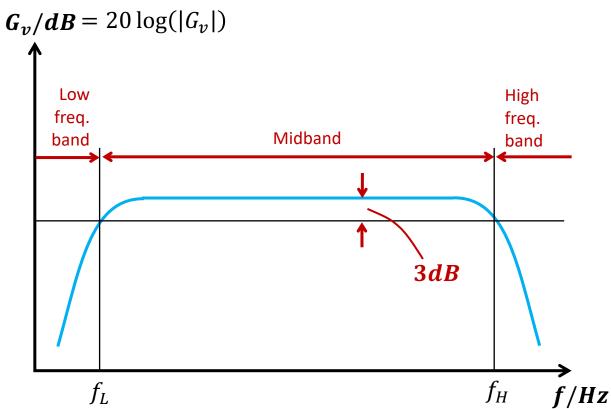

# The Frequency Response

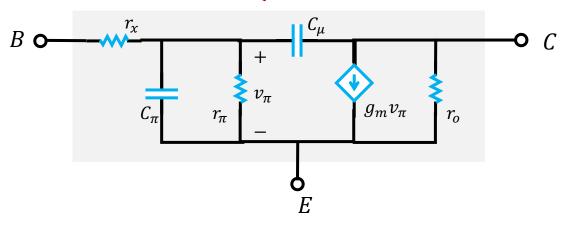

# **Small-Signal Model**

#### SIMPLIFIED HYBRID- $\pi$ MODEL

#### THE HIGH FREQUENCY MODEL

# Recall: Example 5: CE Amplifier

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

# CE Amplifier w/ High Freq. Model

**QUESTION:** Find out the voltage gain, the input and output resistances with given  $v_{in}$ ,  $R_{sig}$ ,  $R_B$ ,  $R_C$ ,  $C_1$ ,  $C_2$ ,  $C_E$ ,  $V_{dd}$ ,  $V_{SS}$ , and  $\beta$ .

We will go through frequency response in details for MOS transistor circuits

#### **Outline**

- Introduction to BJT

- Device structure

- How does it work? 4 modes

- □ npn v.s. pnp

- The characteristic curves

- v = i v characteristics

- The transfer characteristic

- DC analysis techniques

- AC analysis techniques

- The frequency response

#### SIMPLIFIED HYBRID- $\pi$ MODEL

#### SIMPLIFIED T MODEL

# Reading tasks & learning goals

- Reading tasks

- Microelectronic Circuits, 6<sup>th</sup> edition

- Chapter 6

- Learning goals

- Know the structure of a BJT and how it works

- Well understand the characteristic of BJT

- Well understand how to locate the bias point of a BJT in circuit

- Understand how to describe the performance of an amplifier

- Well understand how to analyze a circuit with BJT in active mode

- Know the BJT amplification circuit configuration and analysis